2014_4_23_rodwell_MRS_slides

advertisement

2014 MRS Spring Meeting, April 23, San Francisco.

III-V MOS: Planar and Fin Technologies

M.J.W. Rodwell, UCSB

III-V MOS: S. Lee, C.-Y. Huang, D. Elias, V. Chobpattanna, J. Law,

A.C. Gossard, S. Stemmer, UCSB; T. Kent, A. Kummel, UCSD;

P. McIntyre, Stanford.

Transport Modeling: P. Long, S. Mehrotra,

M. Povolotskyi, G. Klimeck, Purdue

Why III-V MOS ?

III-V vs. Si: Low m*→ higher velocity. Fewer states→ less scattering

→ higher current. Can then trade for lower voltage or smaller FETs.

Problems: Low m*→ less charge. Low m* → more S/D tunneling.

Narrow bandgap→ more band-band tunneling, impact ionization.

Why III-V MOS ? → important but less well-known reasons

nm-precise epitaxy, large heterojunction DEC→ 1nm thick channels

Excellent contacts now.

Better contacts feasible.

Dielectric-channel interface:

Large DEC, no SiO2 at interface→ smaller EOT

-5

10

B=0.3 eV

0.2 eV

0.1 eV

Y-K. Choi et al, VLSI Tech. Symp., 2001

(1nm hard for SOI)

N-InAs

-2

-7

10

-2.5

eV from vacuum level

Contact Resistivity, cm

2

-6

10

-8

10

-9

10

B=0 eV

step-barrier

Landauer

-10

10

18

19

20

21

10

10

10

10

-3

Electron Concentration, cm

-3

-3.5

-4

E

c

-4.5

Si

InGaAs

-5

E

-5.5

-6

v

HfO

TiO

~20

~40

2

r

2

r

http://nano.boisestate.edu/research-areas/gate-oxide-studies/

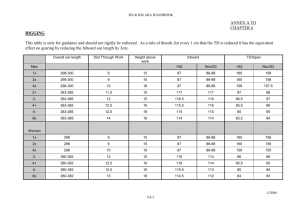

III-V MOS: how small can we make Lg ?

Planar UTB FETs might just scale to 10nm Lg:

nm epitaxial control of channel thickness

high-energy barriers (AlAsSb)

possibly thinner high-K than in Si.

vertical spacer greatly aids short-channel effects

simulations suggest that, with spacers, even S/D tunneling is OK.

And with ALE techniques, few-nm-Lg III-V finFETs are also feasible.

The Key question:

Intel 22nm finFETs Jan, IEDM 2012

Compared to Silicon MOS,...

...can we get high Ion ,

..and low Ioff , and low VDD ,

...at a VLSI-relevant (8-10nm) technology node ?

Performance @ e.g. 35nm is not important !

Small S/D pitch, not just small Lg, is essential !

off-state leakage mechanisms:

Band-band tunneling, S/D tunneling, impact ionization

Small S/D contact pitch

MOS-HEMT with large contact pitch

Current Density (mA/m)

Leakage, short-channel effects, performance comparisons

10

1

10

0

10

-1

10

-2

10

-3

10

-4

10

-5

Lg = 55 nm

VDS = 0.1 to 0.7 V

0.2 V increment

DIBL = 50 mV/V

-6

at VT = 100 A/m

SSmin~ 65 mV/dec. (at VDS = 0.1 V)

SSmin ~ 68 mV/dec. (at VDS = 0.5 V)

10

-0.2 -0.1 0.0 0.1 0.2 0.3 0.4 0.5

Gate Bias (V)

vs.

Lateral depletion region reduces severity of most short-channel effects (not VLSI-compatible)

Leakage, short-channel effects, performance comparisons

off-state leakage mechanisms:

no lateral gate-drain space

Band-band tunneling, S/D tunneling, impact ionization

Small S/D contact pitch

UCSB

MOS-HEMT with large contact pitch

~20 nm gate-drain space

Lin, IEDM2012

Lateral depletion region reduces severity of most short-channel effects (not VLSI-compatible)

Examples from literature: gate-drain lateral spacers

Chang et al.: IEDM 2013:

150nm gate-drain spacer

T. W. Kim et al., IEDM2012

~16 nm S/G, G/D spacers

Lin et al. : IEDM 2013: 70nm S/G, G/D spacers

D. H. Kim et al., IEDM2012

~100nm S/G, G/D spacers

We must build devices with small S/D pitch.

contact pitch ~ 3 times lithographic half-pitch

(technology node dimension)

Small S/D pitch hard to realize if we require ~20-50nm lateral gate-drain spacers !

Vertical spacers: reduced leakage -- at small feasible S/D pitch

vs.

III-V MOSFET development process flow

While our fast development process flow does not provide a small S/D contact pitch,

in manufacturing, the vertical spacer will provide a small S/D contact pitch.

III-V MOSFET development process flow

Simple, 4-day, 16nm process→ learn quickly !

Low-damage: avoids confusing dielectric characterization.

Critical dimensions are scaled: Lg, channel thickness, (N+ S/D):G separations.

Process otherwise not scaled: large gate overlap, large S/D contact separations.

increases gate leakage, increases access resistance.

Process is not now self-aligned, but could be made self-aligned.

TEM Cross-Section, Summer 2013

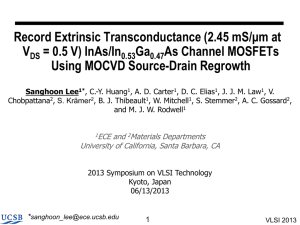

High Transconductance III-V MOSFETS: 2013 VLSI Meeting

1.8

2.8

40 nm

70 nm

90 nm

1.4

2.4

2.0

1.2

1.0

1.6

0.8

1.2

0.6

0.8

0.4

0.2

0.0

VDS = 0.5 V

-0.2

0.0

0.2

0.4

0.6

0.4

0.0

Gate Bias (V)

Ni

3.6 nm HfO2

60 nm

5 nm InAs

3 nm In0.53GaAs

Lg ~40 nm

In0.52AlAs

2.8

2.0

1.6

at Vds=0.5V

D.-H. Kim

2011 IEDM

(HEMT)

2.4

Gm_max (mS/m)

1.6

Gm (mS/m)

Current Density (mA/m)

Lee et al, 2013 VLSI Symposium, May

D.-H. Kim

2012 IEDM

J.J. Gu

2012 IEDM

1.2

T.-W. Kim

2012 VLSI

Intel

2009 IEDM

This work

M. Egard

2011 IEDM

Y. Yonai

2011 IEDM

D.-H. Kim

2012 IEDM

(VDS=1V)

0.8

0.4

0.01

0.1

Gate length (m)

1

8 nm channel (5 nm/3 nm InAs/In0.53Ga0.47As) and ~4 nm HfO2 high-k dielectric

At time, record gm over all gate lengths (i.e. 2.45 mS/μm at 0.5 VDS for 40 nm-Lg)

High Transconductance III-V MOSFETS: 2013 VLSI Meeting

VDS= 0.5 V

400

0.4

VDS= 0.05 V

0.3

300

0.2

200

0.1

100

0.1

Gate length (m)

1

0.0

Current Density (mA/m)

0.5

VTh : Linear extrapolation at Gm_max

1

10

0

10

-1

10

-2

10

-3

10

-4

10

-5

VDS=0.5 V

VDS=0.05 V

40 nm

70 nm

90 nm

-0.2

0.2

0.0

0.4

0.6

Gate Bias (V)

Current Density (mA/m)

500

Threshold Voltage (V)

Subthreshold Swing (mV/dec)

Lee et al, 2013 VLSI Symposium, May

10

10

1

10

0

10

-1

10

-2

10

-3

10

-4

10

-5

10

-6

VDS=0.05 V

VDS=0.5 V

SS ~ 93 mV/dec

at VDS=0.05 V

-0.2

0.0

0.2

0.4

Gate Bias (V)

93 mV/dec @ 500 nm-Lg but > 400 mV/dec @ 40 nm-Lg.

Extremely Poor Short-Channel Effects

0.6

Reducing Leakage: 3nm vs. 8nm High-Field Spacer

result

Reduced off-state leakage, improved short-channel effects, very high gm & Ion.

Current Density (mA/m)

Reducing Leakage: 9nm vs. 7.5nm Channel Thickness

2.0

1.6

VGS = -0.4 V to 1.0 V

0.2 V increment

Ron = 280 Ohm-m

1.2 at VGS = 1.0 V

0.8

0.4

0.0

0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7

Drain Bias (V)

result

Better electrostatics, higher bandgap→ Reduced Ioff, improved subthreshold swing, slightly less gm & Ion.

Vertical spacers: some details

Minimum S/D contact pitch:

depends upon regrowth angle

we need to work on this.

[010] gate orientation should help

Spacer sidewalls are gated through the high-K.

Capacitance to UID sidewalls is negligible.

about 0.2 fF/m

<< the ~1.0fF/m interelectrode capacitances.

Capacitance to N+ contacts layers is large.

easy to eliminate: low-r sidewall spacer.

Deliberate band offset between spacer & channel

compensates offset from strong quantization in channel.

Much Better Results to be Reported

To reduce off-state leakage:

thinner channels (quantization)→ less band-band tunneling

thinner channels & dielectrics → better electrostatics

To increase on-state current:

thinner channels & dielectrics

Much better results to be reported:

Lee et al.: EDL (in press)

Lee et al.: 2014 VLSI Symposium (June)

Thin Wells: Gate Leakage ?

In a thin InGaAs well, does the bound state energy rise

to the point that dielectric leakage becomes high ?

?

-2

eV from vacuum level

-2.5

-3

-3.5

-4

E

c

-4.5

Si

InGaAs

-5

E

-5.5

-6

v

HfO

TiO

~20

~40

2

r

2

r

1.5nm well: (Ebound-Ec)=0.5 eV

Brar data agrees well with:

1) Boykin, APL, 21 March 1994 (simulations)

2) Recent simulations by Povolotskyi (Purdue)

3) Recent unpublished UCSB FET data

Thermal Emission from Source over Back Barrier.

InGaAs-InAlAs barrier is 0.5 eV

Fermi level is 0.3~0.5 eV above

conduction-band in the N+ source.

Barrier is only 0.1~0.25 eV above Fermi

level.

Thermionic emission flux:

J thermionic q (kT / m*)1/ 2 N c exp(( E f Ec ) / kT )

5 A/m 2 for 0.2 eV barrier.

Need increased barrier energy.

Again, effect is less evident in MOS-HEMTs

due to larger N+ S/D separation.

AlAsSb Back Barrier: Stops Barrier Thermal Leakage

InAlAs back barrier

130227C

InAlAs back barrier

60 nm N++

MOCVD RG

InGaAs

60 nm N++

MOCVD RG

InGaAs

AlAsSb back barrier

High-K

10 nm InGaAs channel

400 nm i-InAlAs

SI InP sub

AlAsSb back barrier

120807A

60 nm N++

MOCVD RG

InGaAs

60 nm N++

MOCVD RG

InGaAs

High-K

10 nm InGaAs channel

25 nm i-AlAsSb

375 nm i-InAlAs

SI InP sub

AlAsSb layer:

0.5 eV increase in barrier.

Expect ~108:1 less thermal emission from source.

caution: as-draw gate length and gate widths stated. Data not yet corrected for either.

AlAsSb Back Barrier, P-doped layer, better isolation

2.4

0.2 V increment

2.0

2.0

1.6

1.6

1.2

1.2

0.8

0.8

0.4

0.4

0.0

-0.4 -0.2

0.0

0.2

0.4

0.6

0.0

10

1

10

0

10

-1

10

-2

10

-3

10

-4

10

-5

10

-6

10

-7

0.2 V increment

SS ~ 135.9 mV

at VDS=0.5 V

SS ~ 99.9 mV

at VDS=0.1 V

-0.4 -0.2

Gate Bias (V)

1.4

VDS = 0.1 to 0.7 V

0.0

0.2

0.4

0.6

Current Density (mA/m)

2.4

Current Density (mA/m)

VDS = 0.1 to 0.7 V

Gm (mS/m)

Current Density (mA/m)

InAlAs FET: 88 nm Lg, 25 micron drawn Wg, 8 nm InGaAs channel, 60 nm InGaAs Regrowth, 3.2 nm HfO2, 0 deg

1.2

1.0

0.8

VGS = -0.2 V to 1.6 V

0.2 V increment

Ron = 344 Ohm-m

at VGS = 1.6 V

0.6

0.4

0.2

0.0

0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7

Drain Bias (V)

Gate Bias (V)

2.4

0.2 V increment

2.0

1.6

1.6

1.2

1.2

0.8

0.8

0.4

0.4

0.0

result

-0.4 -0.2

0.0

0.2

0.4

Gate Bias (V)

0.6

0.0

10

0

10

-1

10

-2

10

-3

10

-4

10

-5

10

-6

10

-7

1.4

VDS = 0.1 to 0.7 V

0.2 V increment

SS ~ 115.0 mV

at VDS=0.5 V

SS ~ 91.8 mV

at VDS=0.1 V

-0.4 -0.2

0.0

0.2

0.4

Gate Bias (V)

0.6

Current Density (mA/m)

2.0

10

Current Density (mA/m)

2.4

VDS = 0.1 to 0.7 V

Gm (mS/m)

Current Density (mA/m)

AlAsSb FET: 90 nm Lg, 25 micron drawn Wg, 8 nm

InGaAs channel, 60 nm InGaAs Regrowth, 3.2 nm HfO2, 0 deg

1

1.2

VGS = -0.2 V to 1.6 V

0.2 V increment

1.0 Ron = 388 Ohm-m

at VGS = 1.6 V

0.8

0.6

0.4

0.2

0.0

0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7

Drain Bias (V)

AlAsSb barrier shows lower off-state current and better SS as compared to P-InAlAs barrier.

III-V MOS: how small can we make Lg ?

Planar UTB FETs might just scale to 10nm Lg:

Unlike Si !

nm epitaxial control of channel thickness

high-energy barriers (AlAsSb)

possibly thinner high-K than in Si.

vertical spacer greatly aids short-channel effects

simulations suggest that, with spacers, even S/D tunneling is OK.

And with ALE techniques, few-nm Lg III-V finFETs are also feasible.

Cohen-Elias et al., DRC 2013

FinFETs by Atomic Layer Epitaxy: Why ?

Electrostatics:

body must be thinner than ~Lg /2

→ less than 4 nm thick body for 8 nm Lg

Problem:

threshold becomes sensitive to body thickness

3

Vth Tbody Tbody

Problem:

low mobility unless surfaces are very smooth

6

2

Tbody

/ Tbody

Implication: At sub-8-nm gate length, need :

extremely smooth interfaces

extremely precise control of channel thickness

side benefit: high drive current→ low-voltage, low-power logic

ALE-defined finFET

Fin template: formed by {110}-facet-selective etch→ atomically smooth

Channel thickness set by ALE growth→ atomically precise

Cohen-Elias et al., DRC 2013

HfO2

TiN

Cohen-Elias et al., DRC 2013

channel

10 nm thick fins, 100 nm tall

50 nm fin pitch

fin, ~8nm

100 nm fin pitch

Images

Tall Fins for Low-Power, Low-Voltage Logic

Low-voltage (near-VT ) operation:

low CV2 dissipation, but low current→ long interconnect delays

1000 A/meter

@ V =0mV

100

gs

10

1

0.1A/meter

@ V =0mV

gs

0.1

0

0.1

0.2 0.3

V

gs

0.4

0.5

d

planar FET

I , Amps per meter of FET footprint width

1000

d

I , Amps per meter of FET channel width

Increased fin height→ increased current per unit die area

→ interconnect charging delays reduced

10

4

10

3

10

2

10

1

10

0

10

0.1 A/m

@ Vgs=0mV

1000 A/m

@ Vgs=268mV

finFET:10:1

height/pitch

-1

-0.1 0

0.1 0.2 0.3 0.4 0.5

V

gs

Supply reduced from 500mV to 268 mV while maintaining high speed.

3.5:1 power savings ? Circa 2.5:1 when FET capacitances considered.

What is next ?

In progress:

thinner dielectrics, better contacts, better alignment→ greater Ion

10nm Lg FETs: prove that spacer kills S/D tunneling leakage.

ultra-thin InGaAs & InAs channels low off-current

If we can:

InAs ALE-finFETs @ 10nm Lg→ high performance

110-oriented PMOS finFET→ performance approaching NMOS

29

(end)

Backup slides