Digital Integrated Circuit (IC) Layout and Design

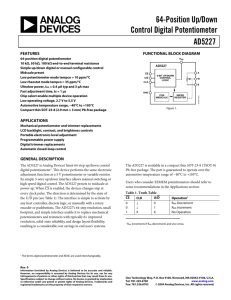

advertisement

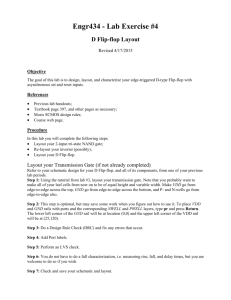

Digital Integrated Circuit (IC) Layout and Design - Lecture 4 ! FIRST LAB this Friday Jan. 20 (tomorrow) ! 2 Lab sections – M 2:10pm – 5pm ENGR2 128 – F 11:10am – 2pm ENGR2 128 http://www.ee.ucr.edu/~rlake/EE134.html 1 EE134 Reading and Prelab " Week 1 ! Read Chapter 1 of text. " Week 2 ! Read Chapter 2 of text. " Prelab ! Read insert A of text, pp. 67 - 71. ! The lab will make more sense if you read this before lab. ! There is nothing to turn in. EE134 2 Agenda " Last Lecture ! MOS manufacturing process ! Design rules " Today’s ! ! ! ! ! ! Lecture MOS manufacturing process Design rules Layout and Design Ties to VDD and GND Padframes Pin Packages 3 EE134 The MOS Transistor Polysilicon EE134 Aluminum 4 CMOS Process Circa 1980s 5 EE134 A Modern Dual-Well CMOS Process silicide layer on poly gate-oxide TiSi2 AlCu SiO2 Tungsten poly p-well n+ SiO2 n-well p-epi p+ p+ DualDual-Well TrenchTrench-Isolated CMOS Process EE134 6 Transistor Layout Cross-sectional view Layout view active n+ EE134 7 N-Well CMOS Flow EE134 8 N-Well CMOS Flow EE134 9 Advanced Metallization EE134 10 Advanced Metallization 11 EE134 Circuit Under Design VDD VDD M2 M4 Vout Vin M1 Vout2 M3 schematic EE134 12 CMOS Inverter Schematic Layout 13 EE134 CMOS Inverter Layout In GND VD D A A’ Out (a) Layout A A’ n p-substrate n+ (b) Cross-Section along A-A’ EE134 p+ Field Oxide 14 Sticks Diagram V DD 3 Out In 1 GND Stick diagrams of inverter EE134 • Dimensionless layout entities • Only topology is important 15 Two Inverters EE134 16 A Different Layout of Same 2 inverters 17 EE134 Design Rules EE134 Design Rules " Interface between designer and process engineer " Guidelines for constructing process masks " Unit dimension: Minimum line width ! scalable design rules: lambda parameter – Less common now ! absolute dimensions (micron rules) – More the standard now. 19 EE134 CMOS Process Layers EE134 Layer Color Well (p,n) Yellow Active Area (n+,p+) Green Select (p+,n+) Green Polysilicon Red Metal1 Blue Metal2 Magenta Contact To Poly Black Contact To Diffusion Black Via Black Representation 20 Layers in 0.25 µm CMOS process 21 EE134 Design Rules " Intra-layer: widths, spacing " Inter-layer: enclosures, overlaps ! Transistor rules ! Contact and via rules ! Well and substrate contacts " Special rules (sub-0.25 µm) ! Area, antenna rules, density rules EE134 22 Intra-Layer Design Rules Same Potential Different Potential 0 or 6 Well 2 9 Polysilicon 2 10 3 Contact or Via Hole 3 2 3 Metal1 Active 2 2 Select 3 4 Metal2 3 23 EE134 Inter Layer: Transistor Layout Self-aligned process Poly-Si Gate p+-active 1 Transistor Channel 3 2 n-well 5 Is this an NMOS or PMOS transistor? EE134 24 Inter Layer: Vias and Contacts • Vias connect metal layer 1 (M1) to metal layer 2 (M2) • Contacts connect M1 to the Si. • Vias and contacts are always square (2x2 µm) •For large area contact, use many “contacts” in an array. 2 4 Via 1 1 5 Metal to Poly Contact Metal to 1 Active Contact 3 2 2 2 25 EE134 Select Layer Select layer reverses the sign of the doping for pinning the substrate to ground (NMOS) or VDD (PMOS) VDD select 2 p+ active select 3 Select n+ 2 1 n+ 3 p+ active 3 Poly-Si Gate n+ 2 5 p+ active n-well p- Substrate EE134 Well 26 Actual Design Rule Example (MOSIS) " http://www.mosis.org http://www.mosis.org/Technical/Designrules/scmos/scmos-active.html EE134 27 Cadence Layout Editor EE134 28 Design Rule Checker poly_not_fet to all_diff minimum spacing = 0.14 um. 29 EE134 2 Types of Checks " Design Rule Checking (DRC) " Layout vs. Schematic (LVS) Schematic EE134 =? Layout 30 DRC and LVS Design Rule Check Schematic Layout Layout vs. Schematic EE134 31 Tie n-well to VDD and Substrate to Ground In GND VD D A A’ Out (a) Layout V VDD A A’ n p-substrate p+ EE134 n+ n+ p+ n+ Field Oxide 32 Reason for GND and VDD Ties Parasitic Diodes Vout p+ n p-substrate n+ VDD n+ p+ n+ p-substrate 33 EE134 Pin n-well to VDD and p-substrate to GND VDD M1 n+ M1 Power Bus Ground Bus GND p+ select EE134 34 Padframe 35 EE134 EE134 0.9 mm 1.5 mm Padframe 36 40 pin package Chip wires Pin Package 37 EE134 Packaging EE134 Packaging Requirements " Electrical: Low parasitics " Mechanical: Reliable and robust " Thermal: Efficient heat removal " Economical: Cheap 39 EE134 Bonding Techniques Wire Bonding Substrate Die Pad Lead Frame EE134 40 Tape-Automated Bonding (TAB) Sprocket hole Film + Pattern Solder Bump Die Test pads Lead frame Substrate (b) Die attachment using solder bumps. Polymer film (a) Polymer Tape with imprinted wiring pattern. 41 EE134 Flip-Chip Bonding Die Solder bumps Interconnect layers Substrate EE134 42 Package-to-Board Interconnect (a) Through-Hole Mounting EE134 (b) Surface Mount 43 Package Types EE134 44 Package Parameters 45 EE134 Flowchart Define circuit specs Circuit Schematic Circuit Simulation Meet Specs? No Layout Parasitic Extraction (R,C) Re-simulate with Parasitics No Meet Specs? Prototype Fabrication Test and Evaluate No EE134 Meet Specs? Yes Production 46