1- Design the schematic to have a minimum AC gain of 60db. Refer

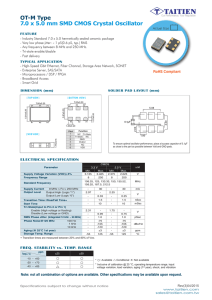

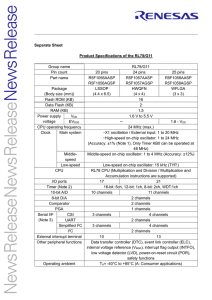

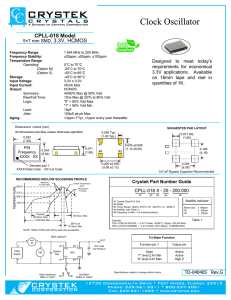

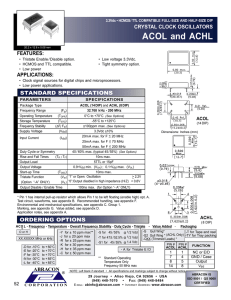

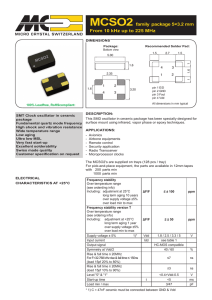

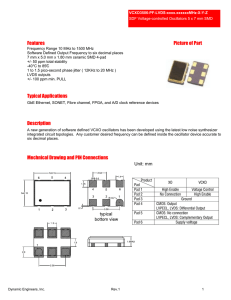

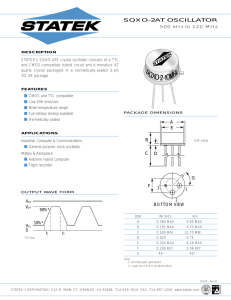

advertisement

Princess Sumaya University for Technology/ The King Abdullah II School for Electrical Engineering. Advanced Electronics - Spring Semester 2011/2012 Due April 8th, 2012 You were hired as design engineer in Jordan’s first IC design start up company. Your hard driving manager asked you to design a two stage OP with the specifications below: 1. 2. 3. Minimum OP DC gain, Ao_OP, is 60dB. (1000). Minimum OP unity gain frequency, ft_OP = 100MHz. Minimum OP Phase margin = 45 degrees. Please show all your work and design methodology. From your simulations, please provide, 1. DC voltages for Nodes (1) - (4)? 2. Widths and Lengths for all devices in the OP? 3. Value for Cc? 4. Value for R? 5. DC Gain of first stage? 6. DC Gain of second stage? 7. Frequencies of Pole (1), Pole (2) and Zero? 8. Is the zero a right hand plane or a left hand plane zero? 9. Slew Rate of OP? 10. Gain Magnitude vs. Frequency plot showing OP DC Gain, Ao_OP and unity gain frequency ft_OP? VDD VDD VDD M6 Node (1) PMOS M8 M5 Vout Node (2) VinM2 200fF M1 AC AC Vin+ 0.9V 0.9V Node (3) 100uA M3 CC R M4 Node (4) NMOS M7 Differential Input First Stage Common Source Second Stage Construct the above schematic using Mentor Graphics software. Requirements and deliverables: 1- Design the schematic to have a minimum AC gain of 60db. Refer to the tutorial on the website. 2- On the schematic, report (W/L) for each transistor, and the DC voltages. 3- Plot AC gain “Vo/Vin” as a function of frequency starting from 1 KHz up to 1 GHz. 4- Run transient simulation for input and output signals having the source’s frequency: 10 KHz, 1 MHz, 10 MHz, 100 MHz and 1 GHZ Notes: 1- Use proper names when plotting the signals. (Refer to the simulation tutorial found on the website). 2- Work should be turned in as HARDCOPY as individuals or as groups with maximum of two students. 3- An extra mark will be added for each of the following: a- The design with the highest gain bandwidth. b- The design with the lowest power consumption. c- The design with the smallest area. (Area = Σ W + Σ L ) 4- Tidy your work and use symbols that contain your Op-Amp. Work should be turned in as IEEE paper format. Eng. Hazem W. Marar