Word file (4.17 MB )

advertisement

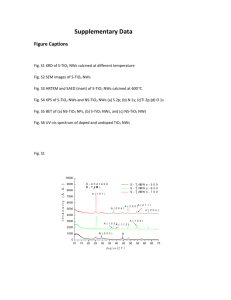

Supplementary Information. 1. Si nanowire structure. The Si NWs typically have lengths of 20-50 m (Fig. S1a) with a nearly mono-dispersed diameter as determined by the Au colloid catalytic particle. As made NWs have a core-shell structure with a single crystalline silicon core surrounded by an amorphous silicon oxide shell1-3 nm thick (Fig. S1b). Fig. S1. (a) Scanning electron microscope (SEM) image of the as-synthesized Si NWs. Scale bar: 10 m. (b) High-resolution transmission electron microscope (TEM) image of the NWs shows a single crystalline core and a ~ 2-nm thick SiOx shell. Scale bar: 5 nm. 2. Fluidic-flow assembly of nanowire thin film over large area. The NW thin film strips were assembled over large area using fluidic-flow alignment approach. Specifically, the as-made NWs were transferred into ethanol using ultra-sonication to obtain a stable NW suspension (Fig. S2a). The NW suspension was then allowed to pass through a fluidic channel structure formed between a poly(dimethylsiloxane) (PDMS) mold and a flat substrate surface to obtain NW arrays on the surface. The average NW space in the thin film was controlled by varying the NW concentration in the solution and/or the total flow time. With this approach, the alignment can be readily extended over 4-inch wafer or even larger areas by using longer/larger flow channel mold. (Fig. S2b,c). Fig. S2. (a) NW solution that was used to do fluidic flow alignment. (b) 4-inch wafer with NWs aligned to the patterned area (the white strips correspond to NW thin film). (c) An optical microscope image of the aligned NW thin film. Scale bar: 20 m. 3. Nanowire core-shell structure for high performance TFTs. The performance of NW-TFTs presented in this work can be further improved in a number of ways by exploiting various NW core-shell structures. First, in NW-TFTs on plastic, the on-off ratio is limited by the low-quality e-beam evaporated AlOx gate dielectrics. This problem can be potentially overcome by using a core-shell NW structure consisting of a single crystal semiconductor core and a high quality gate dielectric shell (Fig. S3a). Although Si NWs naturally have a core-shell structure, the thin native oxide layer is not of enough quality to withstand a high electric field. In future work, the native oxide can be replaced with a high quality silicon oxide shell generated by either controlled thermal oxidation or chemical vapor deposition. We believe that core-shell NW structures will be ideally suited for making high performance NW-TFTs on plastic since it separates all the high temperature processes, including semiconductor material synthesis and high quality gate dielectric formation, from the final device substrate. In addition, such core-shell structure can also lead to passivation of surface trapping states, resulting in further performance enhancement. 2 Second, the current back-gated NW-TFTs are relatively limited in performance (particularly subthreshold swing) due to a geometrical effect. The geometrical effect is caused by non-ideality in NW thin film, which typically consists of nearly a monolayer of NWs, but occasionally with a few NWs crossing over other NWs. When a NW crosses over other NWs in a NW-TFT, it is separated from the substrate surface, experiences a smaller electrical field from the back gate, and thus turns on or off more slowly than other NWs in the device. This increases the subthreshold swing of the NW-TFT as a whole. Such a geometrical effect can be overcome by developing a more complex NW core-shell structure to include a core of single crystal semiconductor, an inner-shell of insulating gate dielectric, and an outer-shell of conducting conformal gate (Fig. S3b). This can be realized by depositing a layer of highly-doped amorphous silicon around the Si/SiOx core-shell structure (described above) as the outer-gate shell. Third, the performance of NW-TFTs can potentially be further improved to exceed that of single crystal materials by exploiting the quantum electronic effect in small diameter NWs. In analogy to conventional two dimensional semiconductor superlattices and 2D electron/hole gas, multi-core-shell NW structure (Fig. S3c) can be envisioned to separate the dopants from the active conducting channel to achieve ultrahigh mobility TFTs (Sakaki, H. Surface Science 267, 623-629 (1992); Tsuchiya, M. et al., Surface Science 267, 296-299 (1992)). 3 Fig. S3. (a) Schematic view of a NW core-shell structure with a crystalline core and integrated dielectric shell. (b) Schematic illustration of a NW structure with a crystalline semiconductor core, an insulating gate dielectric inner-shell and a heavily-doped semiconductor gate outer-shell. (c) Schematic view of a NW structure that separates the dopants from the active conducting channel. The structure consist of an intrinsic semiconductor core (e.g. GaAs), an inner-shell of thin spacing layer (intrinsic material of larger bandgap, e.g. AlGaAs), and an outer-shell of doping layer (doped semiconductor, e.g. n-type AlGaAs). By separating the dopants from the active conducting channel (core) and exploiting quantum-confinement effect, it is possible to achieve very high carrier mobility. 4. CdS nanoribbon structure. Fig. S4. (a) Low-resolution TEM image of a CdS nanoribbon. Scale bar: 2 m. A patterned contrast observed in the TEM image is due to strain resulting from the bending/twisting of the ribbons sitting on TEM grid, which is commonly observed in ribbon-like structures (Pan, Z., Dai, Z., Wang, Z., Science, 291, 1947 (2001)). (b) High resolution TEM image shows that the nanoribbon has a single crystal structure almost free of defects and surface oxide layer. Scale bar: 5 nm. This high crystalline quality explains the exceptional performance of CdS nanoribbon TFT devices. 5. Hysteresis and threshold voltage in Si NW-TFTs. A hysteresis is commonly observed in IDS-VGS relation of the current NW-TFTs (Fig. S5). We believe this hysteresis is primarily due to the surface sates and mobile ions present in our devices, which is well known in conventional MOSFET devices (Wolf, S. et al., Silicon 4 Processing for the VLSI Era - Vol.1 - Process Technology, 2nd Ed. (Lattice Press, Sun Beach, CA, 2000). pp. 291-293). This hysteresis can be eliminated or minimized in the future by stringent control of NW synthesis and device fabrication process to minimize ion contamination and/or surface states. We note that the hysteresis has profound effects in determining threshold voltages. Due to hysteresis, the apparent threshold voltage can vary depending on the measurement condition and the voltage history that the device experienced before measurements. In order to minimize the threshold voltage variation caused by hysteresis, we used exactly the same condition (relatively quick gate voltage sweeping rate of 500 mV/s was used to minimize the mobile ion effect) to test all the devices presented in Fig. 2b main panel and Fig. 2c. Voltage history variation was also minimized by first cycling the gate voltage back and forth (from 10 to -10V) for at least three cycles before collecting data for each device. In this way, we could remove the hysteresis effect in the threshold voltage distribution. On the other hand, in order to accurately measure off-state current, we needed to use a slower gate voltage sweep rate (15 mV/s) to minimize the capacitive current. In this case, the device experienced high positive gate voltage for extended period of time (~5-10min) and shifted the apparent threshold to a more positive value (inset Fig. 2b). Fig. S5. IDS-VGS hysteresis observed in NW-TFT. The arrows indicate gate voltage sweeping direction. 5