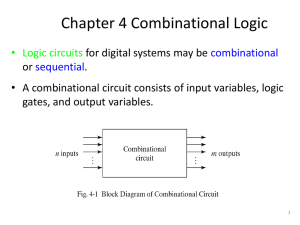

Digital Electronics Chapter 4

advertisement

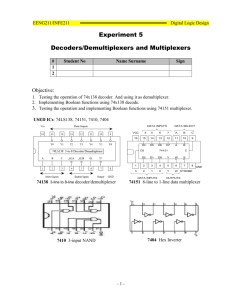

Digital Electronics Chapter 4 Combinational Logic Terminology Combinational:Output is completely determined from the input(s) and does not depend on time Sequential : Output depends on the input(s), previous history, and time Analysis : A circuit is given and one must determine the Truth Table Design: One must build a circuit whose output(s) are given as a Truth Table Analysis Problem Set up the Truth Table Analysis: Truth Table x y F 0 0 0 0 1 1 1 0 1 1 1 0 Design or Synthesis x y z F 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 1 1 1 0 1 1 1 1 1 K-Map of Design Problem y'z' y'z 1 x' x yz yz' 1 1 1 F=xy+xz +yz Final Circuit Design F=xy+xz+yz Binary Adder Half Adder Truth Table x y C S 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 0 Implementation of Half Adder Full Adder x y z C S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 Implementation of Full Adder Magnitude Comparator Comparator Theory x is generated from XNOR and equals 1 if the two bits are equal A = B if all the x’s are equal A > B if the corresponding bit is greater as long as the previous bits are equal A < B if the corresponding bit is smaller as long as the previous bits are equal 3-to-8 Line Decoder Decoder Truth Table Which output will be high when x =1, y = 1 and z = 0 ? Decoder Truth Table Only line 6 will be high. The other 7 lines will be low. Decoder Application Implement the Full Adder with a 3x8 Decoder Full Adder using 3x8 Decoder Important Note! The actual 74LS138 decoder chip has inverted outputs … welcome to the REAL WORLD!!! Multiplexer A multiplexer is a combinational circuit that selects binary information from one of many input lines and directs it to a single output line. Multiplexer Multiplexer Application Implement the function F(x,y,z) = Σ(1,2,6,7) F(x,y,z) = Σ(1,2,6,7) with a multiplexer VHDL // A 2x4 Decoder with enable E module my_decoder (A,B,E,D); input A,B,E; output [0:3] D; assign D[0] = ~(~A & ~B & ~E), D[1] = ~(~A & B & ~E), D[2] = ~(A & ~B & ~E), D[3] = ~(A & B & ~E); endmodule Gate implementation of my_decoder More VHDL ... //A 4-bit comparator module comp(A,B,ALTB,AGTB,AEQB); input [3:0] A,B; output ALTB,AGTB,AEQB; assign ALTB = (A < B), AGTB = (A > B), AEQB = (A == B); endmodule That’s All Folks!