Decoder - Jack Ou

advertisement

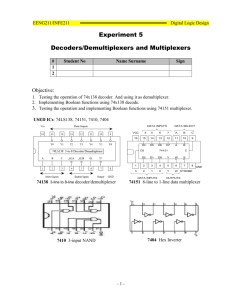

Decoder Mano Section 4.9 Outline • Decoder • Applications • Verilog Example of a Decoder Convert binary information from n input lines to 2n unique output lines. This particular circuit take a binary number and convert it to an octal number. Hardware Implementation AND and NOR Decoders Take an n-bit address. Produce 2n outputs, One of which is activated. (NOR Decoder) Organization of Memory Systems Basic SRAM and VTC A wordline is used to select the cell Bitlines are used to perform read and write operations on the cell Cross Coupled Configuration The cell can only flip its internal state when one of its internal cross VS. During a read op, we must not disturb its current state. During a write op, we must force the internal voltage to swing past VS to change a state. A 2-to-4 decoder with Enable (typo, should be a 0) Demultiplexer A Demux is a circuit that receives information from a single line and directs it to one of 2n possible output lines. Use a 2-to-4 decoder as a Demux Treat A and B as the selector bits. i.e. A and B select which bit should receive infomraiton. E is treated as the data line. (typo, should be a 0) Implement a Full Adder with a Decoder Build a Bigger Decoders Use w to enable either top or bottom decoder. 3-to-8 decoder in verilog 3-to-8 decode Input bits Use a Test Bench to Generate output Initial statements execute once starting from time 0. $monitor: display variable whenever a value changes. $time display the simulation time Run functional Simulation Results