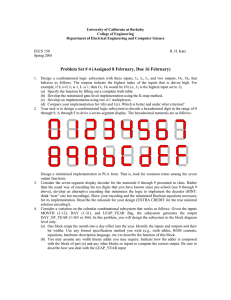

Combinational Circuits

Logic circuits for digital systems may be

Combinational Circuits

Sequential Circuits

Consists of logic gates whose outputs at any time are determined by combining the values of the applied inputs using logical operations.

n inputs

.

.

.

Combinational

Circuit

.

.

.

m outputs

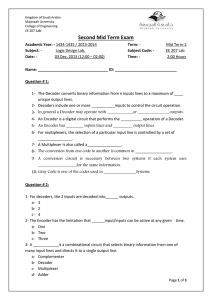

Decoders

Encoders

Counters

Half Adder

Full Adder

Combinational circuit with a number of output lines, only one of which is asserted at any time , dependent on the pattern of input lines.

n inputs and 2 n outputs.

1 2 1 = 2

2 2 2 = 4

3 2 3 = 8

Converts binary information from the n coded inputs to a maximum of 2 n unique outputs.

Larger decoders from small decoders with enable inputs.

3-8 line decoder from 2-4 line decoders

6-64 line decoder from 4-16 line decoders

3-to-8-line decoder constructed from two 2to-4-line decoders

The MSB is connected to the enable inputs if A

2

=0, upper is enabled; if A

2

=1, lower is enabled.

Combinational logic circuit which performs reverse of decoder functions.

Accepts an active level on one of its inputs and converts to a coded output.

The process of converting familiar symbols or numbers to a coded format is called encoding.

Priority Function.

Highest priority takes precedence.