Xilinx_OpenSPARC_Tutorial_1

advertisement

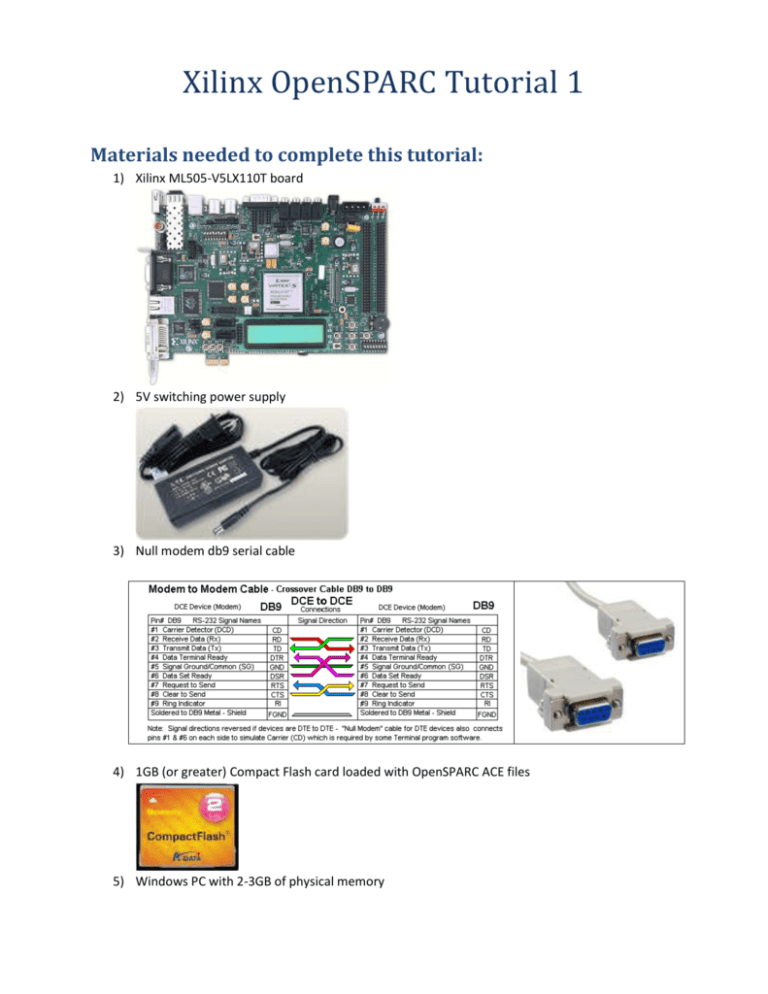

Xilinx OpenSPARC Tutorial 1 Materials needed to complete this tutorial: 1) Xilinx ML505-V5LX110T board 2) 5V switching power supply 3) Null modem db9 serial cable 4) 1GB (or greater) Compact Flash card loaded with OpenSPARC ACE files 5) Windows PC with 2-3GB of physical memory 6) Telnet software such as HyperTerminal included in windows XP or Tera Term Pro 2.3 which can be downloaded from here http://hp.vector.co.jp/authors/VA002416/teraterm.html 7) Xilinx 10.1 ISE and EDK software. http://www.xilinx.com/tools/designtools.htm http://www.xilinx.com/ise/embedded/edk_pstudio.htm 8) OpenSPARC T1 version 1.7 located http://www.opensparc.net/opensparc-t1/download.html 9) OpenSPARC_DVGuide.pdf located in the “doc” folder in the “OpenSPARCT1.1.7” directory in the design downloaded from OpenSPARC web page. 10) (optional) Getting Started Tutorial located at http://www.xilinx.com/products/boards/ml505/reference_designs.htm This guide is not specific for OpenSPARC design but does gives some details of the Xilinx ML505-V5LX110T board. Loading Software Tools: This tutorial was created using windows vista operating system. Download Latest version of OpenSPARC T1 Processor Current version available during creation of this document is 1.7 which has been tested and updated for use with Xilinx ISE and EDK 10.1. Expect 30 minutes to an hour for download. Install Xilinx ISE Design Suite 10.1 This will take some time to download and install. Expect 3-4 hours for download and 1-2 hours for install. You may need to register for trial version if you do not have a copy. Earlier versions are not recommended and later versions are not tested. Install Xilinx EDK Platform Studio 10.1. This will also take some time to download and install. Expect 1-2 hours for download and expect 1-2 for install. You may need to register for trial version if you do not have a copy. Earlier versions are not recommended and later versions are not tested. Install Telnet Software If using Vista or Windows 7 then you must install Tera Term Pro 2.3 or another Telnet program. Windows XP has a Telnet program which is located under start programs Accessories Communications HyperTerminal. HyperTerminal can be ported from XP by copying the “Hyperterm.exe” and “Hypertrm.dll” files to the same directory in windows Vista or Windows 7. Running Hello World ACE file: (Caution should be used when handling board to prevent ESD damage. A static strap is recommended.) 1) Position the Xilinx board so that the Xilinx logo is in the lower right hand corner. 2) Make sure the power switch is in the off position in the upper right hand corner. 3) Locate the CF card slot (on the back side of the ML505 board), and carefully insert the System ACE™ CF card with its front label facing away from the board. The figure below shows the back side of the board with the CF card properly inserted. Note: The CF card provided with your board might differ. Caution! Be careful when inserting or removing the CF card from the slot. Do not force it. 4) Connect the AC power cord to the power supply brick. Plug the power supply adapter cable into the ML505 board at the top right of board. Plug in the power supply to AC power. 5) The SW3 DIP switches on the ML505 board tell the board where to look for the System Ace file. Switches 4-8 select the device that is used to program the system. These switches must be set to 10101 to select the compact flash drive. The typical directory structure of Compact Flash card is 8 directories labeled rev0, rev1, rev2, … rev 7 and switches 1, 2, and 3, tell the system where to look for the System Ace file on the compact flash. A setting of 000 corresponds to the rev0 directory on the compact flash, while setting of 111 selects the rev7 directory. Set the switch for rev0 directory as shown below (00010101). 6) Connect a null modem serial cable between your computer and the ML505 board, and open a serial terminal program. (1) If using Tera term pro 2.3 then the default settings for the com port 1 are already set. Just click “Serial” radial button and then click “OK” to start. (2) If using HyperTerminal then you must setup the com port. First give the new connection a name as shown below. Then Choose Active Com Port. Also provided area code (not to be use later). Fill in port settings as follows and click “OK” Then select FileProperties and select settings tab as shown below. Click “ASCII Setup” and set Character delay to 20 milliseconds. The Click “OK” twice. 7) Turn on the ML505 board’s main power switch and press the SYSACE RESET button located at the lower left of the board. After the FPGA has been programmed, the LEDs in the lower left corner should be: Bus Error 1 and 2 = off FPGA INIT = green FPGA DONE = green System ACE “Err” = off System ACE “Stat” = green Note: When the CF card is ejected or not installed, the System ACE “Err” LED blinks. 8) Verify display below is correct for the terminal window output of Hello World Program. Generating a Bit file for Xilinx FPGA: 1) Read section 6.1-6.4 of the OpenSPARCT1_DVGuide.pdf. This will be used as a reference for the task ahead. Not important to understand everything just yet but read and interpret as much as possible. 2) Prior to generating Bit stream, the windows virtual environment needs to be tweaked to allow for larger than 2 GB virtual memory spaces to be used. To do this in Windows Vista, you must do the following. a) For Windows Vista, reference http://www.xilinx.com/support/answers/32052.htm b) Open a command prompt by going to start and typing cmd in the search text box or located under the start accessories folder. c) Type “BCDEDIT /set increaseuserva 3072” and hit enter; this will increase the user mode application virtual address space to 3GB. Reboot system for new settings to take effect. d) This will correct an error with ISE and EDK which where the application memory space is exceeded and results in a portability error as shown below. e) f) For Windows XP, reference http://www.xilinx.com/support/answers/14932.htm. g) Note: ISE and EDK versions greater than 10.1 may not have this same issue with the virtual memory space. 3) Start Xilinx EDK platform Studio. 4) Open file “System.xmp” located in (root directory)\design\sys\edk\system.xmp 5) Select menu option Hardware Generate Bit Stream 6) This will take about 2-3 hrs to build and generate if no errors occur. 7) Tutorial 1 is complete.