Chapter 1 VLSI Design Methods

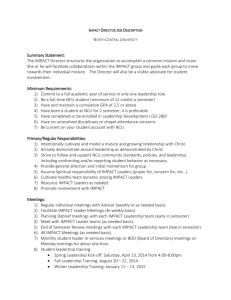

advertisement

Chapter 1 VLSI Design Methods Jin-Fu Li Advanced Reliable Systems (ARES) Laboratory Department of Electrical Engineering National Central University Jhongli, Taiwan Outline Introduction VLSI Design Flows & Design Verification VLSI Design Styles System-on-Chip Design Methodology Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 2 Complexity & Productivity Growth of ICs Complexity grows 58%/yr (doubles every 18 mos) Productivity grows 21%/yr (doubles every 31/2 yrs) unless methodology is updated Complexity and Productivity Growth 10,000,000 100,000,000 1,000,000 10,000,000 Productivity 100,000 1,000,000 10,000 100,000 1,000 10,000 100 1,000 10 1980 Advanced Reliable Systems (ARES) Lab. Produc tiv ity Tra ns is tors /Sta ff M onth C om ple xity Tra ns istors per C hip (K ) Com plexity 100 1985 1990 1995 2000 2005 Jin-Fu Li, EE, NCU 2010 [Source: MITRE] 3 VLSI Design Methodologies Design methodology Process for creating a design Methodology goals Design cycle Complexity Performance Reuse Reliability Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 4 IC Community Design rules Silicon Simulation models and parameters IC foundry Mask layouts design Integrated circuits CAD Process information tool Software tools provider [M. M. Vai, VLSI design] Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 5 System to Silicon Design System Requirements Algorithm Hardware Architecture Synthesis X[k] = Σ x[n]e-j2 πk/N System Integration x[n] = Σ X[k]e+j2 πk/N Σ Fabricate and Test Physical Design For Test Observe Co nt ro l [Source: MITRE] Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 6 Y-Chart Structural Domain Behavioral Domain Processor Algorithm Register ALU FSM Module Description Leaf Cell Transistor Boolean Equ. Mask Cell Placement Module Placement Chip Floorplan Physical Domain Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 7 VLSI Design Flow Concept Design Validation RTL Verification Logic Verification Designer Final Product Behavior Specification Manufacturing Behavior Synthesis Layout (Masks) RTL Design Layout Synthesis Logic Synthesis Netlist (Logic Gates) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU Product Verification Layout Verification 8 Behavioral Synthesis & RTL Synthesis 4 cycles=16 ns Behavioral Synthesis 3 cycles=15 ns Vary clock period HDL Vary # clock cycles z = a(i) × b(i) − c × d (k ) + f 2 cycles=20 ns Multiple Architectures RTL Synthesis 1 cycle=50 ns Vary clock period 1 clock cycle Single Architecture Source: Synopsys Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 9 Behavioral Synthesis (Resource Allocation) Source code defines the functionality y_real := a_real * b_real - a_imag * b_imag y_imag := a_real * b_imag + a_imag * b_real Constraints allow designer to explore different architectures, trading off speed vs. area Two possible implementations for a complex multiplier: Fast, but large Small, but slow (4 mult, 1 add, 1 sub) (1 mult, 1 add/sub) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU [Source: MITRE] 10 Behavioral Synthesis (Retiming) Allows designer to trade off latency for throughput by adding and moving registers in order to meet timing constraints Specification needs to include registers at functional boundaries, without regard to register-to-register timing: software takes care of optimizing register placement Compiled Functional Description Circuit After Behavioral Retiming > create_clock clk -period 10 > pipeline_design -stages 3 register tp = 0.5 > optimize_registers tp=5 tp=23.0 tp=8.7 tp=9.5 Max. Speed= 1/23.0 nSec = 43 MHz Max. Speed= 1/10 nSec = 100 MHz Latency Latency = 1 clock cycle Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU = 3 clock cycles [Source: MITRE] 11 Verification The four representations of the design Behavioral, RTL, gate level, and layout In mapping the design from one phase to another, it is likely that some errors are produced Caused by the CAD tools or human mishandling of the tools Usually, simulation is used for verification, although more recently, formal verification has been gaining in importance Two types of simulations are used to verify the design Functional simulation & timing simulation Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 12 DFT Flow Behavioral Description Behavioral DFT Synthesis RTL Description Technology Mapping Layout Logic DFT Synthesis Gate Description Parameter Extraction Manufacturing Test Pattern Generation Low Gate Fault Coverage ? Product Test Application High Good Product Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 13 Design Styles – Full Custom A B Z Vss Vdd z B A Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 14 Design Styles – Programmable Logic Array AND array OR array Buffering Buffering Outputs Inputs Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 15 Design Styles – Gate Array Cell 1 Cell 2 Cell 3 Cell 4 Cell 5 Cell 6 Cell 7 Cell 8 Cell 9 Cell 10 Cell 11 Cell 12 Cell 13 Cell 14 Cell 15 Cell 16 Cell 17 Cell 18 Cell 19 Cell 20 Cell 21 Cell 22 Cell 23 Cell 24 Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 16 Design Styles – Field Programmable Gate Array (FPGA) Xilinx SRAM-based FPGA Configurable Logic Block (CLB) I/O Block Routing channel Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 17 Design Styles – Field Programmable Gate Array (FPGA) Xilinx XC4000 Configurable logic block Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 18 Design Styles – Field Programmable Gate Array (FPGA) SRAM-based programmable switch Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 19 Design Styles – Field Programmable Gate Array (FPGA) Architecture of Altera FLEX 10K FPGA FastTrack Interconnect I/O I/O I/O I/O EAB Logic Array Block (LAB) I/O I/O I/O I/O Embedded Array Block I/O EAB I/O I/O Advanced Reliable Systems (ARES) Lab. I/O Jin-Fu Li, EE, NCU 20 Design Styles – Field Programmable Gate Array (FPGA) Logic array block Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 21 Standard-Cell Design Styles Cell 1 Cell 6 Cell 2 Cell 7 Cell 8 Cell 13 Advanced Reliable Systems (ARES) Lab. Cell 3 Cell 4 Cell 9 Cell 14 Cell 5 Cell 10 Cell 11 Cell 12 Cell 15 Cell 16 Cell 17 Jin-Fu Li, EE, NCU 22 Standard-Cell Design Styles Design entry Enter the design into an ASIC design system, either using a hardware description language (HDL) or schematic entry An example of Verilog HDL module fadder(sum,cout,a,b,ci); output sum, cout; input a, b, ci; reg sum, cout; ci always @(a or b or ci) begin sum = a^b^ci; cout = (a&b)|(b&ci)|(ci&a); end endmodule Advanced Reliable Systems (ARES) Lab. b a fadder cout sum Jin-Fu Li, EE, NCU 23 Design Styles – Comparison Design Styles Advantages Disadvantages Full-custom - Compact designs; - Improved electrical characteristics; - Very time consuming; - More error prone; Semi-custom -Well-tested standard cells which can be shared between users; -Good for bottom-up design; -Can be time consuming to built-up standard cells; -Expensive in the short term but cheaper in long-term costs; -Fast implementation; -Easy updates; -Can be wasteful of space and pin connections; -Relatively expensive in large volumes; FPGA Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 24 Emergence of SOC Idea Motivation: Transistor density Moor's law Integration with analog parts AMS specification, synthesis, simulation SoC Design Methodology and Tools Filling the Gap through Source: Synopsys Reuse Design Automation System Specification Methodology Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 25 What’s a System? System [Source: M. Gudarzi] Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 26 What’s a System? Customer’s view: System = User/Customer-specified functionality + requirements in terms of: Cost, Speed, Power, Dimensions, Weight, … Designer’s view: System = HW components +SW modules [Source: M. Gudarzi] Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 27 Hierarchical Design Flow for an System Chip Specification Hardware Architecture Detail Design Requirements and specification Architecture Hardware Design Software Design Specification Software Architecture Module Design Integration Integration Integration Test System test Test Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 28 HDL’s & SDL’s: Requirements HDL’s HardwareC Verilog AHDL VHDL SDL’s C Pascal ADA [Source: M. Gudarzi] Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 29 HDL’s & SDL’s: Realization Hardware Program Software Program Compilation Synthesis Operating System [Source: M. Gudarzi] Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 30 HDL’s & SDL’s: Features Any SW-realizable algorithm is HW-realizable as well. Hardware Realization Software Realization Speed Energy Efficiency Cost Efficiency (in high volumes) Flexibility Ease of Development Ease of Test and Debug Cost = SW + Processor [Source: M. Gudarzi] Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 31 HW-SW Co-design How much SW + how much HW? Objectives: Power Speed Area Memory space Time-to-market Implementation platform: Collection of chips on a board (MCM) … Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 32 HW/SW Co-Design Methodology Must architect hardware and software together: provide sufficient resources; avoid software bottlenecks. Can build pieces somewhat independently, but integration is major step. Also requires bottom-up feedback Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 33 HW/SW Co-design Main Topics Synthesis System H System S OS Specification Verification [Source: M. Gudarzi] Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 34 [Source: M. Gudarzi] System Specification Verification Co-Synthesis Partitioning HW Parameter SW Parameter Estimation Estimation HW Synthesis Verification SW Synthesis Verification ASIC OS EXE Code Advanced Reliable Systems (ARES) Lab. System Integration Jin-Fu Li, EE, NCU Verification Final Verification 35 SOC Design Essentials Realization strategy: Automated HW-SW Co-design + Reusable Cores Intellectual Property: IP Cores IP Core Examples: Processors: PowerPC, 680x0, ARM, … Controllers: PCI, … DSP Processors: TI ... IP Core Categories: Soft Cores: HDL, SW/HW Cores Firm Cores: Synthesized HDL Hard Cores: Layout for a specific fabrication process Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 36 Trends and Challenges of SOC Designs Technology trends 3D technology + System-in-package Architecture trends Regular architectures, e.g., multi-core architecture Network-on-chip communication Challenges Power Reliability Yield Design-for-manufacturability … Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 37