INVERTER LAYOUT BY L-EDIT

advertisement

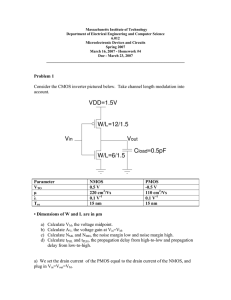

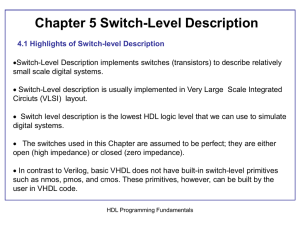

INVERTER LAYOUT BY L-EDIT Website and how to download STEP 1 – Launch L-Edit 1. Before launch L-Edit, make sure it running in the 256 colors condition. If not, right click the icon and click on ‘Properties’, then select ‘ Run in the 256 colors’ in the ‘Compatibility’ tab. 2. Run L-Edit. The following window will open up. STEP 2 – Create new Layout file 1. File > New. 2. In the following open window, Browse and choose ‘mamin08.tdb’ in ‘Copy TDB setup from file’ area. It usually locates in ~\stu712\mosis\. 3. From Setup > Design, the relationship between Lambda and Microns is shown. Now the technology is setup. In this introduction, I will layout a simple inverter with PMOS sized L = 2 Lambda, W = 12 Lambda and NMOS sized L = 2 Lambda, W = 6 Lambda. Show them these DR on web MOSIC STEP 3 – Draw PMOS 1. Choose N-Well in the left palette and draw a box. 2. In the N-Well area, draw P-Select. Notice that the size and position should obey Design Rule, which can be found at http://www.mosis.org/Technical/Layermaps/lm-scmos_scnpc.html. With the help of DRC button , the violation of design rule can be shown by right click the place where is violate the design rule. It is a good idea to run DRC at each stage of your design so that you can fix any error along the way 3. Draw Active. 4. Draw Poly. STEP 4 – Draw NMOS 1. Do not need to draw P-Well because the empty grid of L-Edit stands for P-Well. 2. Draw N-Select. 3. Draw Active. 4. Draw Poly. contacts STEP 5 – Draw VDD and GND 1. Choose Metal1 in the left palette and draw box as shown. STEP 6 – Connect bulk to substrate 1. For PMOS, place a small N-Select on the N-Well, add a small Active layer. From this active layer put contacts to the Metal1 layer that connects to VDD. 2. For NMOS, on the P-Well substrate, place a small P-Select and then Active layer. From this active layer put contacts to the Metal1 layer that connects to GND. STEP 7 – Connections 1. Connect Poly of PMOS and NMOS. 2. Connect source of PMOS to VDD by Metal 1. 3. Connect source of NMOS to GND by Metal 1. 4. Connect Drain of PMOS and NMOS by Metal 1. 5. Add an input connect between Metal1 and Poly. STEP 8 – Label Label the INPUT, OUTPUT, VDD and GND using button. STEP 9 – Run DRC finally 1. Run DRC for the total layout. 2. Fix the errors listed. 3. Once there is no DRC error shown, the layout is ready to be extracted.