415mw2003

advertisement

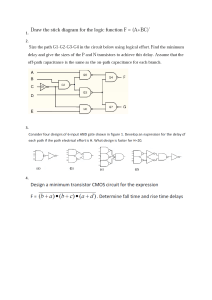

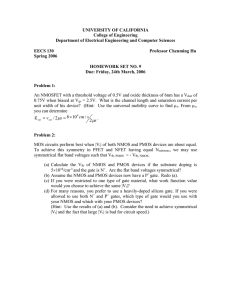

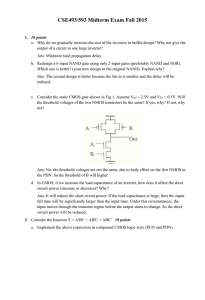

EE 415/515 VLSI DESIGN Dr. J.A. Starzyk MIDTERM - DURATION TIME 50 MINUTES Saturday, February 13, 2016 THIS IS A CLOSED BOOK EXAM Name: Box #: Note: 1) All scratch and problem papers must be turned in. 2) Estimated times required to complete problems are indicated. Problem Weight Estimated Time Examiner' Use (points) (minutes) only ________________________________________________________ 1 10 15 2 10 20 3 10 15 _________________________________________________________ TOTAL 30 50 _________________________________________________________ Problem 1 For given circuit shown below, answer the following questions. a. What is the logic function implemented by the CMOS transistor network? Size the NMOS and PMOS devices so that the output resistance is the same as that of an inverter with an NMOS W/L = 4 and PMOS W/L = 8. b. What are the input patterns that give the worst case tpHL and tpLH. State clearly what are the initial input patterns and which input(s) has to make a transition in order to achieve this maximum propagation delay. Consider the effect of the capacitances at the internal nodes. Problem 2 Assume that you are working with 0.25mm technology and use minimum length gates. Answer following questions a. Draw the schematic corresponding to the layout. Include transistor sizes. b. What logic function does the circuit implement? Problem 3 Assume that you are working with 0.25mm technology. Answer following questions a. Determine the size of NMOS and PMOS transistors b. Determine the combined output capacitance of this inverter Use the following parameters: Cox Co Cj(fF/m2) (fF/m2) (fF/m) mj b(V) Cjsw (fF/m) mjsw bsw (V) NMOS 6 0.31 2 0.5 0.9 0.28 0.44 0.9 PMOS 6 0.27 1.9 0.48 0.9 0.22 0.32 0.9