Lab 9 FSM - People.vcu.edu

Lab 9

Design of a FSM counter circuit using 74LS107 flip-flops.

Assigned

Design due

Circuit demonstration

Wednesday 4/1/09

Thursday 4/2/09

Thursday 4/2/08 or

Thursday 4/9/08 with 15 point penality.

For this lab, work with a partner. No lab report is required, but turn in this signoff sheet. You have two weeks to fabricate and demonstrate your design; however, if you do not successfully demonstrate your design during lab on April 2 nd

15 points will be deducted from your grade.

You cannot run over into the next lab session to complete your fabrication. If you have not successfully demonstrated your design by the end of the lab session, you will have to complete it next week and will be subject to the 15 point penalty.

Name: ______________________________, ______________________________,

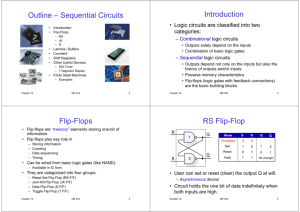

Using

74LS107

JK flip-flops, and standard gates design, implement, and demonstrate the FSM with the state table shown below. For the demonstration wire up your circuit on the CADET breadboard. Use a switch to control X, and connect a second switch to the asynchronous /CLR inputs of the 74LS107. Use this switch to put the circuit in the initial

“000” state. Connect the CLK inputs to the square wave oscillator on the CADET. When testing the circuit notice how the /CLR switch can be used to hold the FSM in state

“000”.

X

State Q

2

Q

1

Q

0

0 1

S0

S1

S2

S3

S4

S5

S6

000

001

010

011

100

101

110

001

011

001

111

000 ddd

100

100

100

001

111

010 ddd

100

S7 111 110 110

1.

Prelab

Q maps.

Signoff: _____________

2.

J and K equations for each flip-flop.

Signoff: _____________

3.

Correctly annotated Orcad schematic.

Signoff: _____________

Problems with schematic?

NO YES Time: _________

Wire up and demonstrate your design.

Use Q

2

, Q

1

, and Q

0

for outputs and connect these to LED’s on the CADET. Use SWT 1 for X, and use the TTL output of the CADET oscillator for the Clock. The circuit for this lab is more complex that those you have done before, and the clock input to the flip-flops respond to very fast transitions. It is important to use good fabrication techniques. Keep your wire leads short and be sure to use .01 uF bypass capacitors on all IC’s. Connect all of the /CLR inputs of the JK flip-flops together and connect this to a switch on the

CADET. Demonstrate your design to the instructor or TA.

Test 1: Set X = 0, and using the /CLR switch put the state in “000”. Verify that the output sequence is: 0, 1, 3, 7, 6, 4, 0, …

Test 2: Set X = 1, and using the /CLR switch put the state in “000”. Verify that the output sequence is: 0, 4, 2, 1, 4, …

Signoff for demonstration: ___________________________________________

Date:

4/2/09 4/9/09 Time: ___________

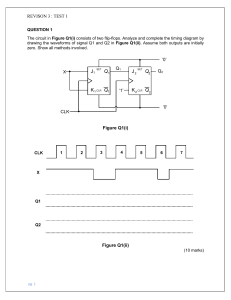

Partial Schematic:

U1A

12

13

1

4

J

K

CLK

CLR

Q

Q

3

2

Q2

74LS107

U1B

8

11

9

10

J

K

CLK

CLR

74LS107

Q

Q

5

6

Q1

CLK

/RESET

U2A

1

4

12

13

J

K

CLK

CLR

74LS107

Q

Q

3

2

Q0