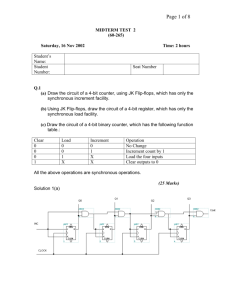

Outline – Sequential Circuits q Introduction Flip-Flops RS Flip-Flop

advertisement

Introduction Outline – Sequential q Circuits • • • Logic circuits are classified into two categories: t i Introduction Flip-Flops – RS – JK – D • • • • – Combinational logic g circuits • Outputs solely depend on the inputs g g gates • Combination of basic logic Latches / Buffers Counters Shift Registers Other Useful Devices – Sequential logic circuits • Outputs depend not only on the inputs but also the history of outputs and/or inputs. • Possess memory characteristics • Flip-flops (logic gates with feedback connections) are the basic building g blocks – 555 Timer – 7-Segment Display • Finite State Machines – Examples Chapter 7b ME 534 2 Chapter 7b Flip-Flops p p ME 534 RS Flip-Flop p p • Flip-flops are “memory” elements storing one-bit of information. • Flip-flops play key role in – – – – 3 Prohibited Storing information Counting Data sequencing Timing No change! • Can be wired from basic logic gates (like NAND). – Available in IC form. • User can set or reset (clear) the output Q at will. • They are categorized into four groups: – – – – Reset-Set Flip-Flop (RS F/F) Jam Kill Flip Jam-Kill Flip-Flop Flop (JK F/F) Data Flip-Flop (D F/F) Toggle Flip-Flop (T F/F) Chapter 7b ME 534 – Asynchronous device • Circuit holds the one bit of data indefinitely when both inputs p are high. g 4 Chapter 7b ME 534 5 JK Flip-Flop p p Clocked RS Flip-Flop p p 3 1 • CLK S R Q Q Prohibited 1 1 1 - - Set 1 1 0 1 0 Reset 1 0 1 0 1 Hold 1 0 0 Disabled 0 2 4 • Mode – J (jam) sets the output state, Q – K (kill) iinputt resets t it. it • Device updates its states at the instant when the clock signal goes from either No change! No change! – Inputs are in effect when the clock signal goes high. ME 534 6 Chapter 7b Pulse Generators of JK F/F Positive-Edge Trigger: CLK Inverter with delay A Y 7 Positive-Edge Triggered: Negative-Edge Triggered: Inverter with delay A CLK Y B B d l delay t t delay t t t ME 534 J K Q Q Toggle 1 1 Q Q Mode t t Chapter 7b ME 534 Operating p g Modes of JK F/F Negative-Edge Trigger: CLK – Low to high g logic g state (positive edge triggered) OR – High to low logic state (negative edge triggered) triggered). Pulse generator emits a pulse at the transition points of the clock signal allowing inputs take effect for a short duration of time. Clock coordinates the actions of independent units in a complex logic circuit. Clocked RS F/F operates in a synchronous fashion. Chapter 7b • JK F/F is considered as universal flip-flop. Set 1 0 1 0 Reset 0 1 0 1 Hold 0 0 No change! * * * * * * No change! Hold 0 Hold 1 Hold 8 CLK Chapter 7b No change! No change! g ME 534 9 JK F/F with Clear & Preset D Flip-Flop p p Level Triggered: Edge Triggered: I 7476 In 4 6 (double (d bl F/F F/Fs iin chip), hi ) PR and d CLR inputs i are to set and d reset the output states of the device in an asynchronous fashion. Chapter 7b ME 534 10 Chapter 7b ME 534 D F/F with Clear & Preset Mode PR CLR CLK D Q Latch • Latch is a collection of levelsensitive iti D fli flip-flops. fl Q – Captures n-bit data. – Stores data which is to be later used by slower devices. Prohibited N change! No h ! 7475 IIn 7474 4 4 (double (d bl F/F F/Fs iin chip), hi ) PR and d CLR inputs i are to set and d reset the output states of the device in an asynchronous fashion. Chapter 7b 11 ME 534 D0 Q0 D1 Q0 D2 Q1 D3 Q1 E0-1 E2-3 12 Chapter 7b ME 534 13 Tri-state Buffers • C When several devices share the same data transfer line (bus) (bus), the connections of an inactive device must be electrically isolated during this idle period i d tto protect t t allll devices d i ffrom short-circuiting. Three-state buffers or so-called tristate buffers are employed for this purpose: Y A Counters • – They have one (electrically-controlled) (electrically controlled) state called “high impedance.” (HI) – At that time, the connection of inactive device appears to be severed: • A very high impedance is observed by external circuitry. Chapter 7b ME 534 14 • Counters are used to count events like clock pulses. They can be utilized to – Divide frequency – Store data • Digital counters are selected considering the following attributes: – – – – – Maximum number of counts (in bits) BCD vs. binary Up / down count Asynchronous or synchronous operation Free-running or self-stopping Chapter 7b ME 534 4-bit BCD Counter 4-bit Ripple pp Counter Vcc = 5V Q0 J CLK J FF1 K Chapter 7b J FF2 Q K 1s CLR CLK Q0 Q1 Q2 Q3 Q Q J FF3 Q K 2s • 74192 is a synchronous y decimal ((BCD)) binary-coded up/down counter. • When the clock is connected to the UP pin pin, it counts up. Q3 Q2 Q1 Q Q FF4 Q K Q – Unused clock pin (DN or UP) must be tied to Vcc. Vcc 4s 8s (Power pins are not illustrated) 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0000 0001 5 13 14 15 1 0 1 2 3 4 6 7 8 9 10 11 12 0 ME 534 15 16 Chapter 7b • Initial states of the flip-flop are loaded from the data input pins when LD is 0 0. • Counter can be reset when CLR = 1. • Several counters could be cascaded for higher-order counting counting. ME 534 17 Two Decimal-Digit g Counting g Resetting g Counters Vcc Vcc = 5V U1:74192 Vcc Vcc = 5V U1:74192 CLK U2:74192 I3 Q3 I3 Q3 I2 I1 I0 Q2 Q1 Q0 I2 I1 I0 Q2 Q1 Q0 LD CLR UP DN LD CLR UP DN B C 10s CLK U2:74192 I3 Q3 I3 Q3 I2 I1 I0 Q2 Q1 Q0 I2 I1 I0 Q2 Q1 Q0 LD CLR UP DN 1s LD CLR UP DN B C 10s B C B C External logic elements are employed to reset the counters ( y, 60). ) automaticallyy when a certain count value is reached (say, Chapter 7b ME 534 18 Chapter 7b Popular p ICs 74279: 74279 7474: 7475 7475: 7476: 74125 74125: 74163: 74192 74192: 7493: Chapter 7b 19 Shift Registers g • Shift registers are used for sequencing and interfacing between serial and parallel communication systems. • Binary sequence is shifted left or right at each clock pulse. Quad Q d SR Fli Flip-Flop Fl Dual D-type Flip Flop 4 bit L 4-bit Latch t h Dual JK-type Flip Flop Ti t t B Tri-state Buffer ff 4-bit Binary Counter 4 bit BCD C 4-bit Counter t 4-bit Binary Counter ME 534 ME 534 – While shifting, g the register g must hold the content of the shifted data. • The registers are classified as – – – – 20 Chapter 7b Serial-in serial-out (SISO) shift registers Parallel-in serial-out (PISO) shift registers Serial in parallel Serial-in parallel-out out (SIPO) shift registers Parallel-in parallel-out register (or simply “register”) ME 534 21 Shift Registers g 4-bit SISO ((Right) g ) Shift Register g Serial in / Serial out: Parallel in Parallel in / Serial out: 1 0 1 1 0 1 0 0 1 0 1 1 0 1 0 0 Serial in / Parallel out: Serial S i l outt 0 0 1 ... Parallel out 1 0 1 1 0 1 0 0 Serial in ... 0 1 0 1 0 1 1 0 1 0 0 Chapter 7b ME 534 22 Chapter 7b D Q FF1 Q3 D Q FF2 Q2 D Q FF3 Q1 D Q Serial Input Q0 FF4 Chapter 7b Q3 Q2 Q1 Q0 ME 534 • Some comercially available shift registers are – 7495: 4-bit shift register – 74164: 74164 8-bit 8 bit serial i l iin, parallel ll l outt – 74165: 8-bit serial/parallel-in serial out – 74195: 4-bit parallel access Clock Serial out 23 Shift Register g ICs 4-bit SISO ((Left)) Shift Register g Serial Output ME 534 Serial in 24 Chapter 7b ME 534 25 Timers LM555 VCC VCC U1: 555 • R Reliable li bl timing ti i source, which hi h iis tto synchronize h i th the operation of various units of the circuit, is needed in digital circuits circuits. • For simple logic circuits, 555 timer, which has a timing range from μs to minutes, is utilized. • It has two operation modes: Vout The p parameters of the circuit are determined using the following expressions: 10nF 1 GND 2 Trig. Dischg. 7 3 Out Thres. 6 4 Reset Ctrl. 5 Vcc VCC = +5V 8 RA tH = 0.695( RA + RB )C RB + 10 F 10nF + – Astable ((free running) g) multivibrator – Mono-stable (one-shot) multivibrator tL = 0.695 RBC C f = • The timing parameters of the device is adjusted via two resistances and a capacitor. Chapter 7b ME 534 26 Schmitt Trigger gg as Clock Source Chapter 7b 1.44 0.695( RA + 2RB )C ME 534 27 7414 Schmitt Trigger gg ((Cont’d)) Vout 5V • Schmitt trigger incorporates a hysteresis loop (relay) and is frequently employed: Vin VT- Vin VT+ 4 3.5 5 Voltage e [V] Vout Vin Voltage [V] 4 With R and C values, one can select the oscillation frequency of output voltage waveform: 3 2 VT+ (1.7 V) ((0.9 V)) VTT 1 fosc 0 0 Chapter 7b 5 4.5 – to filter glitches – to shape up slowly varying signals • For time-insensitive applications, an inverting Schmitt trigger (like 7414) could be utilized to generate a clock signal. R = 1 MΩ ; C = 1 μF Vout ME 534 1 2 3 4 5 Time [s] 6 7 8 9 1 = 0.853 ⋅ RC 3 25 2.5 Vout 2 1.5 Vin 1 0.5 0 0 05 0.5 1 15 1.5 2 25 2.5 Time [s] 3 35 3.5 4 45 4.5 5 10 28 Chapter 7b ME 534 29 7 Segment g Displays p y Seven-segment g Decoder Common Anode: (LS 5025) U:7447 A0 A1 A2 A3 BCD Number LT BI LED Test Common Cathode: (LS 5015) Blanking RBI Ripple Blanking a b c d e f g (Power pins are not illustrated) Chapter 7b ME 534 30 Chapter 7b Example p – 7 Segment g Display p y cc • 7447 decoder is frequently used to drive a 7-segment display. • Input to the decoder is a 4bit BCD. • Its outputs are connected to the corresponding pins off a (common-anode) ( d )7 7segment display. • Display is active when all control inputs are high. ME 534 31 Finite State Machines cc • Logic circuits with memory – Outputs = f(inputs, past inputs, past outputs) – Such circuits have finite states: 0 • State indicates the state of a memory device (F/Fs) in circuit. • State is generally an input or an output to a combinational logic circuit. 1 2 3 – Circuit goes thru a sequence of states in a cycle cycle. • Different actions are performed at each state. – Example: Door combination lock Chapter 7b ME 534 32 Chapter 7b ME 534 33 FSM Architectures State Transition Diagrams g Two types of FSM architectures are commonly used: Moore FSM: Mealy FSM: X=* Register D1 X=* X=*/Y=* Q1 1 D2 D1 Q1 X=*/Y=* DN DN Q2 • State transition diagrams (STD) are used to visualize/analyze the operation of an FSM. FSM – Each state (S) is represented by a circle. – Transition from one state to I=*/Y=* another is indicated an arrow. 2 QN QN 4 3 X=* Cl k Clock X=* Clock Chapter 7b ME 534 34 Chapter 7b FSM Model • Corresponding p g inputs p ((X)) necessary to make that transition happen are shown above the arrows. • Proceeding P di a slash, l h output t t (Y) at the present state is also given. ME 534 35 Design g Procedure These connections are made if applicable. Next States X1 NS1 D1 Present S States Q1 X2 XI NS2 D2 Q2 PS1 • Begin with circuit function specifications • • Draw state transition diagram (STD) Create state transition table (STT) – Verbal V b ld description i ti off th the circuit’s i it’ operation ti Y1 Y2 – Tabular form f off state diagram – Very similar to truth table PS2 • NSN DN QN PSN YJ Decide on the representation of the states (a.k.a. “state encoding”) – Use counters whenever possible • Simplifies the design D F/F – Create encoded STT • • Clock • • • D (Data) F/F is associated with each encoded state. state Combinational input logic generates next set of states. Outputs depend on present states of machine. Derive Boolean expressions for each state Draw circuit diagram – F/F for each state – Design combinatorial logic circuits to implement encoding – If necessary, necessary inputs are taken into consideration. consideration Chapter 7b ME 534 36 Chapter 7b ME 534 37 Example p 1* Solution • Before a new bit arrives, the circuit needs to remember whether the number of bits in previous “step” is even or odd. • A natural choice for f the states is – Even (0) and Odd (1) • Design a circuit for odd-parity checking: – Accepts a bit stream as input. – If the number of ones in the stream is odd odd, the output becomes high (1). Chapter 7b ME 534 [*] CS-150 Class Notes, UC Berkeley. 38 Chapter 7b Solution (Cont’d) ( ) State Transition Table: ME 534 39 Example p 2* Boolean Expression: • Design the FSM of a newspaper dispenser. di NS = PS ⊕ IN OUT = PS S – Each newspaper is, say, 15¢. – Exact change is required to get the newspaper: • 5¢ (“Nickel”) (“ ”) + 10 10¢ (“Dime”) (“ ”) • 5¢ + 5¢ + 5¢ p of 2×10¢ ¢ is also • A deposit accepted but no nickel is returned! – With correct change, the lock of the dispenser is to be released. Chapter 7b ME 534 40 Chapter 7b ME 534 [*] CS-150 Class Notes, UC Berkeley. 41 Solution Solution (Cont’d) ( ) • Inputs: N (Nickel) and D (Dime) • • States: St t 0¢ 5¢, 0¢, 5¢ 10¢, 10¢ and d 15¢ 15¢. Output: OPEN – Lock mechanism generates RESET. PS S D N NS S 0 0 0¢ 0 1 5¢ 1 0 10¢ 0 0 5¢ 0 1 10¢ 1 0 15¢ 0 Chapter 7b 0 10¢ 0 1 1 1 15¢ 15¢ - - 15¢ ¢ • Let us uniquely encode 4 states using two F/Fs: OPEN O ME 534 – D1 and D0 are their data inputs (Next states). – Q1 and Q0 are their outputs (Present states). • • • • 42 Solution (Cont’d) ( ) Examining STT closely yields Chapter 7b 0 0 1 1 NS Q0 0 1 0 1 D N D1 D0 0 0 0 0 0 1 0 1 1 0 1 0 0 0 0 1 0 1 1 0 1 0 1 1 0 0 1 0 0 1 1 1 1 0 1 1 - - 1 1 ME 534 OPEN 0 0 0 1 43 One-hot ((State)) Encoding g Circuit Schematics: • Thanks to its simplicity, one one-hot hot state encoding are often-time employed in digital circuit design: D1 = Q1 + Q0 N + D D0 = Q1 ( N + D ) + Q0 ' N + Q0 N ' – One D F/F for each state of the FSM – Easy encoding – Simplifies derivation of Boolean expressions OPEN = Q1Q0 Note that a FSM must be initiallized correctly Hence correctly. Hence, Set and Reset inputs of D F/Fs are used to set the initial states of the circuit. Chapter 7b 0¢ → Q1 = 0; Q0 = 0 5¢ → Q1 = 0; Q0 = 1 10¢ → Q1 = 1; Q0 = 0 15¢ → Q1 = 1; Q0 = 1 PS Q1 • During the operation of the circuit, only one state is active (“hot”) ( hot ) while the remaining ones are inactive (“cool”). • Not N t very efficient ffi i t utilization tili ti off resources. ME 534 44 Chapter 7b ME 534 45 Example p 2 - Revisited • This time, four states will be encoded using four F/Fs: • • • • Q3 0 0 0 1 Present States Q2 Q1 0 0 1 0 1 0 0 Chapter 7b 0 0¢ 5¢ 10¢ 15¢ Q0 1 0 0 0 → Q3 = 0; Q2 = 0; Q1 = 0; Q0 = 1 → Q3 = 0; Q2 = 0; Q1 = 1; Q0 = 0 → Q3 = 0; Q2 = 1; Q1 = 0; Q0 = 0 → Q3 = 1; Q2 = 0; Q1 = 0; Q0 = 0 Next States D1 D2 Boolean Terms: D N D3 0 0 0 0 0 1 0 1 0 0 1 0 1 0 0 1 0 0 0 0 0 0 1 0 0 1 0 1 0 0 1 0 1 0 0 0 D2 = Q0 D + Q1 N + Q2 D' N ' 0 0 0 1 0 0 D3 = Q1 D + Q2 ( D + N ) + Q3 D0 0 1 1 0 0 0 1 0 1 0 0 0 - - 1 0 0 0 ME 534 OPEN 0 0 0 D0 = Q0 D' N ' D1 = Q0 N + Q1 D' N ' OPEN = Q3 1 46