CEBDBDEACAF + + + = b) Given the pull

advertisement

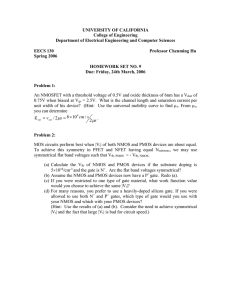

UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences Andrei Vladimirescu Homework #6 Due Monday, March 12th, 5pm @ 558 Cory EECS 141 Problem 1: Static CMOS gate design a) What is the function of the gate? (F=?) F = A C + A E D + BD + B E C b) Given the pull-down NMOS network, draw the Euler Path diagram for both NMOS and PMOS network See diagram below. c) Design the Pull-up Network with PMOS only transistors. See diagram below. Vdd E Vdd B A A B C D E F F Gnd C E A C B D D F Problem 2: CPL gate design a) As shown in Figure 2 on the next page, what’s the function of the CPL circuit? Description only, not logic equation. It’s 2-to-1 mux, with C as the select, and A, B as the two inputs b) What’s the purpose of the PMOS? They a pair of cross coupled level restorer c) Given Vdd = 2.5V, and equivalent resistance Rn(W=1)= Rp(W=2) = 10kOhm, what’s the static power consumption of the gate? (Assume the inputs are from similar CPL gates with inverters as output buffers) If A and A! does not arrive at the same time, there will be at least one conducting path between Vdd and Gnd, which consist of the PMOS transistor, NMOS pass transistor and the input Inverter gate NMOS transistor. So total equivalent resistance of 30kOhm, so power is V2 P = dd = 208.33µW R d) If the buffer inverters has the high noise margin of 0.625V, what’s the minimum size of the PMOS? 0.625V is ¼ of the total swing range of 2.5V, so the PMOS has to be weak enough for the final input high voltage to the buffer inverter to fit into the high noise margin, 2 Wp 1 thus ≤ ⇒ Wp ≥ 3 2 Wp + 1 +1 4 Problem 3: DCVSL gate design (Figure 3) a) Design the NMOS pull-down network for a DCVSL gate, which implements F = ABC + A B + AD , along with the complementary output. You can assume all inputs also have their complementary signals available. (If you can implement the pull-down network in less than 10 transistors, you will get 10% extra credit of this homework) The best solution has only 9 transistors in the pull-down network, shown below. b) Identify the worse case delay when only one of the four inputs transitions. Specify the type of the input transition and the input pattern of the rest three inputs. With the circuit shown above, the worse case is when A=1, either B or C is 1 while the other make a 1-to-0 transition; D can be either 0 or 1. If you implemented the circuit differently in part a) you may have a different worse case.