Homework #2

advertisement

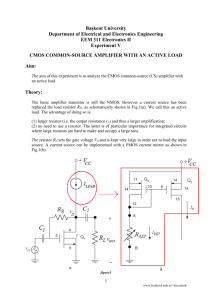

UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences Andrei Vladimirescu Homework #2 Due Thursday, February 3, 5pm @240 Cory EECS141 Problem 1 – Extracting Unified Model Parameters from Simulation The objective of this problem is to simulate a complex transistor model using SPICE, extract fundamental information from the results to build an approximate transistor model for use in hand calculations, and then compare the two models. 1A Using SPICE, generate the family of I-V curves for an NMOS transistor with the following parameters: W/L = 10u/0.5u Sweep VDS from 0V to 2.0V in 0.1V increments VGS = 0.4V, 0.8V, 1.2V, 1.6V, 2.0V VSB = 0V, 1.0V Use the 0.25um model by adding the following line to your SPICE deck or copying the same file to your own account or workstation: .lib ‘/home/ff/ee141/MODELS/g25.mod’ TT 1B Based on the results from the previous part, determine the following model parameters: VT0, kp, , . You may assume that velocity saturation doesn’t play a significant role and -2F = 0.6V. Which parts of the characteristic are the most important to be matched? 1C Starting with the SPICE deck used in the first part, add your own simple transistor model using the parameters determined above. This should be of the form .model nmos_simple NMOS (LEVEL = 1 + VT0=?? KP=?? GAMMA=?? LAMBDA=?? PHI=0.6) Generate the family of I-V curves for an NMOS transistor with the following parameters, showing simulation of both the original model and your own simplified model on the same plot. Comment on any differences. W/L = 10u/0.5u Sweep VDS from 0V to 2.0V in 0.1V increments VGS = 0.5V, 1.0V, 1.5V, 2.0V VSB = 0.8V Problem 2 – Generating a Voltage Transfer Characteristic The circuit below features an NMOS transistor that is coupled to a non-linear load device represented by the shaded box. Accompanying the figure is the I-V characteristic for this non-linear load device. 2.5V Vout Vin 2A Draw the VTC for this circuit. Determine (or estimate, if necessary, from your VTC) the following parameters: VOH, VOL, VM. 2B This circuit can be used as an alternative to a traditional CMOS inverter (where the non-linear device is a PMOS transistor). From the concepts discussed thus far in lecture and from the results of your VTC, what are the disadvantages of this method? The family of I-V curves for the NMOS transistor is given below: Problem 3 – VTC and Inverter Analysis A “Psuedo NMOS” inverter implementation is shown in Figure A, in which the load is a PMOS transistor with a fixed VGS. Figure B shows a saturated inverter used in NMOS technology and Figure C shows a standard CMOS inverter. 3A 3B Find VOH, VOL, and VM for the thtee inverters using the quadratic equations. Use HSPICE to plot the VTC of the three inverters. Compare the differences in the VTC curves, robustness, and regeneration (assuming the output will connect to another inverter of the same implementation) of the two inverters. Fig. A Fig. B Fig. C Vdd=2.5V Vdd=2.5V W/L=1u/0.5u 0.5u/0.5u Vout Vin W/L=1.5u/0.5u W/L=3u/0.5u Vin 2u/0.5u Vout W/L=1u/0.5u Use the following parameters: NMOS: VT0=0.5V, kp=18uA/V2, =0.5V1/2, =0.06V-1 PMOS: VT0=0.5V, kp=5uA/V2, =0.5V1/2, =0.1V-1 Problem 4 – Propagation Delay and Technology scaling Evaluate the propagation delay through the three inverters shown in the above figure assuming a load capacitance CL = 100fF and that each inverter is driven by an identical inverter. 4A Use the switch approximation of the MOS transistor presented in class (Req is average of Rmid and R0) to estimate tpLH, tpHL and the average propagation delay, tp. 4B Verify tpLH and tpHL with HSPICE in one case just with the parameters known from problem 1 and in the second case adding the parameter TOX=20nm. Explain the difference. 4C In order to get a good estimate of propagation delay it is customary to use a ring oscillator; estimate the propagation delay in 0.25u technology and then verify your result using the parameters in the file ‘~ee141/MODELS/g25.mod’. Use minimum length devices and a three times wider PMOS device.