Analysis and Design of Digital Integrated Circuits

advertisement

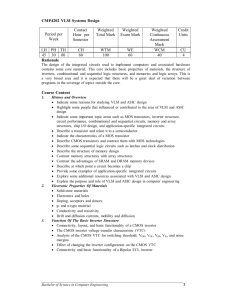

TEACHING ARCHIVESTIEI Course Description (for 2014) Course Description Tianjin International Engineering Institute Course Name(Chinese):数字集成电路分析与设计 (English):Analysis and Design of Digital Integrated Circuits Course Name: Analysis and Design of Digital Integrated Circuits Course Code: Semester: 2 Credit: Programme: Electronic Course Module: Specialized Subjects Responsible: Shi Zaifeng E-mail: shizaifeng@tju.edu.cn Department: School of Electronic Information Engineering Time Layout (1 credit hour = 45 minutes) Practice Lecture Lab-study 8 24 16 Project Internship(days) Personal Work 32 Course Resume This course examines the device and circuit level optimization of digital building blocks. Topics covered include: MOS device models including Deep Sub-Micron effects; Circuit design styles for logic, arithmetic and sequential blocks; Estimation and minimization of energy consumption; Interconnect models and parasitics; Device sizing and logical effort; Timing issues (clock skew and jitter) and active clock distribution techniques; Memory architectures, circuits (sense amplifiers) and devices; Testing of integrated circuits. Pre-requirements Digital Logic Circuit;electronic circuit and system Course Objectives This course covers the analysis and design of digital integrated circuits using CMOS technology. The course emphasizes design, and requires extensive use of MAGIC for circuit layout, and HSPICE and IRSIM for simulations. -1- TEACHING ARCHIVESTIEI Course Description (for 2014) Course Syllabus 1.Challenges in Digital IC Design: Course Overview 2.CMOS Inverter I: 2.1 MOS Device Model with Sub-micron Effects; 2.2 VTC Parameters - DC Characteristics 3.CMOS Inverter II 3.1 CMOS Propagation Delay 3.2 Parasitic Capacitance Estimation 3.3 Layout of an Inverter 3.4 Supply and Threshold Voltage Scaling 3.5 SPICE Simulation Techniques 4.CMOS Inverter III 4.1Components of Energy and Power 4.2 Switching, Short-Circuit and Leakage Components 4.3 SPICE Simulation Techniques 5.Combinational Logic I 5.1 Static CMOS Construction 5.2 Rationed Logic 6.Combinational Logic II 6.1 Pass Transistor / Transmission Gate Logic 6.2 DCVSL 6.3 Introduction to Dynamic Logic 7.Combinational Logic III 7.1Dynamic Logic Design Considerations 7.2Power Dissipation in CMOS 8.Combinational Logic IV 8.1 Power Consumption in CMOS Logic (cont.) 8.2 Leakage Power Dissipation 8.3 Logical Effort Sizing - Performance Optimization of Digital Circuits 9.Arithmetic Structures / Bit Slice Design 9.1 Adders, Multipliers, Shifters 9.2 Design Methodology 9.3 Layout Techniques and Mapping 9.4 Project Schedule and Guidelines 10.Evening Session on Exploring Project Ideas; Finish Arithmetic Structures and Project Ideas 11.Guest Lecture by Prof. TayoAkinwande: Integrated CMOS Processing 12.Sequential Circuits I 12.1 Classification / Parameters 12.2 Static Latches and Register 13.Sequential Circuits II 13.1 Race Condition 13.2 Dynamic Latches and Registers 13.3 Two Phase vs. Single Phase 14.Sequential Circuits III -2- TEACHING ARCHIVESTIEI Course Description (for 2014) 14.1Pulse Based Registers 14.2 Latch vs. Register Systems 14.3 Metastability 15.Interconnect 15.1 Capacitance Estimation 15.2 Buffer Chains 15.3 Low Swing Drivers 15.4 Power Distribution 15.5 Issues in Timing - Impact of Clock Skew and Jitter 16.Clock Distribution 16.1 Origins of Clock Skew / Jitter and Impact on Performance 16.2 Clock Distribution Techniques 16.3 Self-timed Circuits 17.Memory I: ROM / EPROM / PLA Design 17.1 Organization / Architecture 17.2 Cell Design 17.3 Sense-amplifiers 17.4 PLA Folding Techniques 17.5 Self-timing 18.Memory II: SRAM Design 18.1 Cell Design 18.2 Differential Sense Amplifiers 18.3 Self-timing 19.Memory III 19.1 DRAM Design 19.2 Single Ended Sense Amplifier 19.3 CMOS Scaling 20.Advanced Voltage Scaling Techniques 20.1 DC-DC Converter Design 20.2 Performance Feedback 20.3 Dynamic Voltage / Frequency Scaling 21.Power Reduction Through Switching Activity Reduction Testing in VLSI 21.1 Defects, Fault Models, Path Sensitization 21.2 Scan, Built-in-self Test, IDDQ Text Book & References Required: Rabaey, Jan, AnanthaChandrakasan, and Bora Nikolic. Digital Integrated Circuits: A Design Perspective. 2nd ed. Prentice Hall, 2002. Capability Tasks CT1 CT2 CT3 CT4 CT10 -3- TEACHING ARCHIVESTIEI Course Description (for 2014) Achievements To be able to use MAGIC for circuit layout design.-Level: M To be able to use HSPICE and IRSIM for simulations - Level: M Students: Electronic year 2 -4-