Lecture 3: Boolean Algebra I * the basics

advertisement

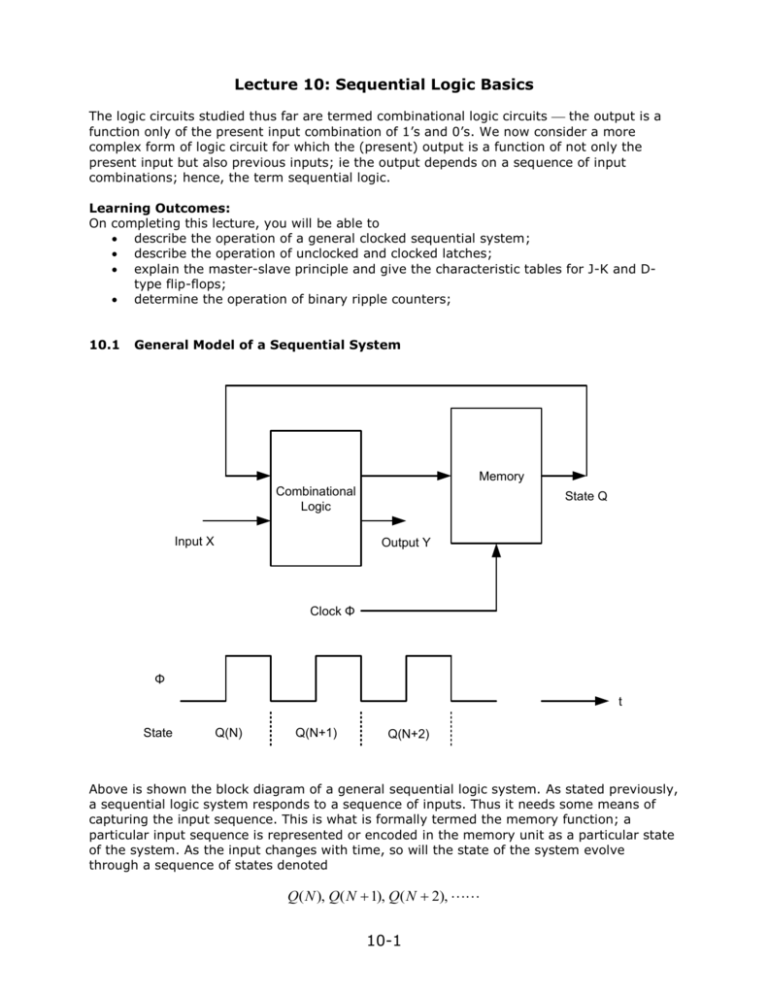

Lecture 10: Sequential Logic Basics The logic circuits studied thus far are termed combinational logic circuits the output is a function only of the present input combination of 1’s and 0’s. We now consider a more complex form of logic circuit for which the (present) output is a function of not only the present input but also previous inputs; ie the output depends on a sequence of input combinations; hence, the term sequential logic. Learning Outcomes: On completing this lecture, you will be able to describe the operation of a general clocked sequential system; describe the operation of unclocked and clocked latches; explain the master-slave principle and give the characteristic tables for J-K and Dtype flip-flops; determine the operation of binary ripple counters; 10.1 General Model of a Sequential System Memory Combinational Logic Input X State Q Output Y Clock Φ Φ t State Q(N) Q(N+1) Q(N+2) Above is shown the block diagram of a general sequential logic system. As stated previously, a sequential logic system responds to a sequence of inputs. Thus it needs some means of capturing the input sequence. This is what is formally termed the memory function; a particular input sequence is represented or encoded in the memory unit as a particular state of the system. As the input changes with time, so will the state of the system evolve through a sequence of states denoted Q( N ), Q( N 1), Q( N 2), 10-1 The sequencing of events in time is controlled by means of a clock signal , a periodic train of 1’s and 0’s. Changes of state are only allowed to occur once per clock cycle and only at a particular point in the clock cycle, normally either the 0-to-1 transition or the 1-to-0 transition, as in the diagram above. A combinational logic circuit monitors the system input X and the present state of the system Q(N), and in turn produces (i) the system output Y, and (ii) a signal to the memory to set the next state Q(N+1). Sequential logic systems and components invariably comprise combinational logic circuits with a feedback loop. 10.2 Bistable Latches The bistable latch is the basic building block for the memory unit. Our approach will be to present the logic diagram for a bistable and then explain how the logic functions rather than attempting to design the bistable logic from scratch. S Q P R Consider the logic circuit shown. There are two inputs, S and R, and two outputs, Q and P. With two inputs, there are four possible input combinations which we now consider, but not in the usual binary incrementing manner: (i) S=1 R=0 The S = 1 condition forces Q = 1, which, together with R = 0, forces P = 0 With Q = 1 and P = 0, the latch is said to be in the set state. (ii) S=0 R=1 The R = 1 condition forces P = 1, which, together with S = 0, forces Q = 0 With Q = 0 and P = 1, the latch is said to be in the reset state. (iii) S=0 R=0 Either the set state (Q = 1, P = 0) or the reset state (Q = 0, P = 1) is possible as a solution; basically, the latch will remain in the state corresponding to whichever of S or R most recently had a 1 on its input. (iv) S=1 R=1 This input combination forces the outputs into the Q = 1 and P = 1 state; the previous complementary output property is lost, ie P no longer equals Q. For this practical reason, the input condition S = 1 and R = 1 is not normally allowed. 10-2 A more serious problem with the S = 1 and R =1 input condition arises in the event of both inputs simultaneously reverting to 0. What happens then is that both outputs are driven towards 0 and a race condition results whereby the first to 0 will drive the other back to 1. The final state of the circuit, set or reset, is uncertain. This a further reason for not using the S = R = 1 input mode. S Q R Q' In summary then, the SR-latch has a setting input S, and a resetting input R; the latch remembers which input most recently had a 1. For technical reasons, we agree not to simultaneously try to both set and reset the latch; ie we rule out the S = 1 and R = 1 input possibility and hence we can replace the P output by Q as shown in the latch symbol above. As noted earlier, digital systems are generally synchronised to a clock signal, which basically should mean that only one event (change of state) may occur per clock cycle and at a precise point in the cycle. As a first step in linking our bistable latch with a clock, we propose: S Q S Φ Q C R Q' Q' R Clearly the action of setting or resetting this device can only occur when clock signal is high. This device is what known as the clocked latch. = 1, ie when the The final latch that we introduce is one which is built in such a way as to ensure that the S=1 R=1 condition does not occur. This is the D-type latch: D Q D Q C Q' Φ Q' 10-3 If D= 1 then D = 0 then the latch sets when =1 the latch resets when =1 From the point of view of a clocked sequential system, the flaw with all these clocked latches is that they can change state many times when the clock is high, as many times as the data inputs might change when the clock is high. 10.3 The Master-Slave Principle and Flip-Flops The basic objective here is to come up with a clocked bistable device which can change state once and only once per clock cycle, and at a well-defined point in the cycle. Master Latch D D Q C Q' Slave Latch X D Q Q C Q' Q' Φ Φ D X Q Consider the two-latch system shown above and the illustrative signal waveforms. Note in particular the complementary clocking arrangement; when the clock to the first latch, the so-called master latch, is high, the clock to the secondary latch, or slave latch, is low; and vice versa. We describe the device operation relative to an individual clock pulse as follows: When =1 the master latch is enabled; its output X goes into the same state as input D; with =0, the slave latch cannot change state; it holds the same state it was originally in, ie output Q holds its initial state. When =0 The master latch is now disabled; it cannot change state; X holds the state it was in when the clock was high; with = 1, the slave latch is now enabled; it goes into the same state as X. 10-4 Essentially then, the device senses the D input when = 1, while the main output Q holds its initial value; when the clock goes low, the state of the master latch transfers to the slave latch; ie the new output state appears at the moment the clock makes the transition from high to low. We note in particular that this master-slave device can only make one ouput transition in a clock cycle. The descriptive term flip-flop is used for such a device. We summarise D-type flip-flop operation by means of what is known as the characteristic table: D = D(N) 0 0 1 1 Q(N) 0 1 0 1 Q(N+1) 0 0 1 1 where D(N) and Q(N) represent, respectively, the input and state of the flip-flop before the active transition of the N-th clock pulse and Q(N+1) represents the state of the output after the clock transition. The operation is also captured by the equation Q( N 1) D( N ) The flip-flop has the symbol D C Q Φ Q' Q(N+1) Q(N) Another very common and useful device is the JK flip-flop: J D D Q Q Q' Q' K C Φ Noting that D JQ ( N ) K Q( N ) where D, J, and K are understood to denote values before the clock transition, we can construct the characteristic table as follows: 10-5 J K Q(N) D JQ ( N ) K Q( N ) Q(N+1) 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 0 1 1 1 0 0 1 0 0 1 1 1 0 This is usually given in the more compact form J 0 0 1 1 K 0 1 0 1 Q(N+1) Q(N) 0 1 Q(N) Comment No change f-f resets f-f sets f-f reverses state The JK flip-flop is depicted J Q C Q' K 10.4 Asynchronous Counters Binary counters are extremely important logic modules, finding numerous application in microprocessors, instrumentation, analogue-digital converters, etc. Asynchronous, or ripple, counters are built from JK flip-flops and exploit the feature whereby J=K=1 causes the device to change state. We first consider a binary counter having a range/scale that is an integral power of two. 1 1 J In Q J C K 1 Q J C Q' K Q0 C Q' K Q1 10-6 Q Q' Q2 In Q0 Q1 Q2 000 001 010 011 100 101 110 111 Every pulse on the line marked “In” causes the first flip-flop in the chain, that having Q0 as output, to change state on the falling edge of the In pulse. Similarly, every pulse on the Q 0 line causes Q1 to change state, again on the falling edge of the Q0 pulse. Q2 is generated in a similar manner from Q1. When we then look at the sequence of binary numbers formed from Q2 Q1 Q0, we note a sequence counting from zero through to seven and then back to zero. Clearly, by adding further flip-flops the count range can be extended. If we consider the transition from 111 back to 000, we see that the 1-to-0 In transition causes the 1-to-0 Q0 transition, in turn causing the 1-to-0 Q1 transition, etc. This ripple through effect gives the system the name ripple counter. It is also called an asynchronous counter because, if we take propagation delays into account, the flip-flops do not all change state at precisely the same moment in time. Nevertheless, asynchronous counters with a range that is an integral power of two are very simple and straightforward units. If we want a range that is not an integral power of two, then the logic has to be amended. The following example is that of an asynchronous decade counter; ie it cycles from 0000 through to 1001 and then back to 0000. J In Q J C K 1 Q J C Q' K C Q' K 1 Q0 X Q 10-7 Q C Q' K 1 Q1 J Q' 1 Q2 Q3 In Q0 Q1 Q2 X Q3 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 Q0 switches over on every falling edge of the input pulses. Q1 switches over on every falling edge of Q0 provided Q3=0; if Q3=1, denoting the count is eight or greater, Q1 remains reset. Q2 switches over on every falling edge of Q1. Q3 changes from 0 to 1 when Q2 and Q1 are both 1 and on the falling edge of Q0; this in effect gives the transition from 0111 to 1000; Q3 resets to 0 on the next falling edge of Q0 so that the sequence runs from 1001 to 0000. 10.5 Conclusion In this lecture, having explained the basic idea of a clocked digital system, we have introduced the family of bistable devices, beginning with the latch and developing through to D-type and JK master-slave flip-flops. Asynchronous binary counters have been treated as examples of simple sequential logic systems but having very wide applicability. 10-8