Chapter 5 - MyWeb at WIT - Wentworth Institute of Technology

advertisement

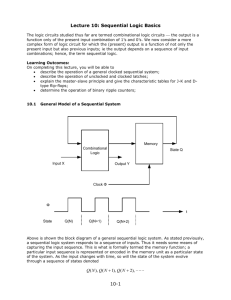

Digital Logic Chapter 5 Presented by Prof Tim Johnson Wentworth Institute of Technology Department of Electrical Engineering and Tech. Boston, MA Text: Digital Systems by Ronald Tocci Introduction to Chapter 5 Logic circuits studied so far have outputs that respond immediately to inputs at some instant in time. We now introduce the concept of memory. The flip-flop, abbreviated FF, is a key memory element. The outputs of a flip flop are Q and Q Q is understood to be the normal output, Q is always the opposite. When the normal output (Q) is placed in the high or 1 state we say the FF has been set. When the normal output (Q) is placed in the low or 0 state we say the FF has been cleared or reset. NAND Latch: Info The NAND gate latch or simply latch is a basic FF. Two NAND gates are cross-coupled so that the output of NAND-1 is connected to one of the inputs of NAND-2, and vice versa. The gate outputs, Q and Q , are the latch outputs. Under normal conditions, these two outputs will always be the inverse of each other. There are two inputs: SET 0 Q 1 (Q 0) RESET 0 Q 0 (Q 1) NAND Latch: Function Table The SET and RESET inputs are active low. The output will change when the input is pulsed low. NAND Latch: Waveform Determine the waveform for Q for the inputs given below. Assume that initially Q = 0. NAND Latch: Block Symbol Alternate Representation Simplified Block Symbol NOR Latch: Info The NOR latch is also a basic FF. Two NOR gates are cross-coupled so that the output of NOR-1 is connected to one of the inputs of NOR2, and vice versa. The arrangement of a NOR latch, as shown below, is similar to a NAND latch except that the Q and Q outputs have reversed positions. SET 1 Q 1 (Q 0) RESET 1 Q 0 (Q 1) NOR Latch: Function Table NOR Latch Function Table Simplified Block Symbol The SET and RESET inputs are active high. The output will change when the input is pulsed high. NOR Latch: Waveform Determine the Q waveform for the NOR latch. Assume that initially Q = 0. Digital Pulses Signals that switch between active and inactive states are called pulse waveforms. The transition from low to high on a positive pulse is called rise time (tr). A positive pulse has an active high level. A negative pulse has an active low level. Rise time is measured between the 10% and 90% points on the leading edge of the voltage waveform. The transition from high to low on a positive pulse is called fall time (tf). Fall time is measured between the 90% and 10% points on the trailing edge of the voltage waveform. Digital Pulses: Rise and Fall Times Clock Signals and Clocked FFs Asynchronous system – outputs can change state at any time the input(s) change. Synchronous system – output can change state only at a specific time in the clock cycle. The clock signal is a rectangular pulse train or square wave. Positive going transition (PGT) – when clock pulse 0 1 Negative going transition (NGT) – when clock pulse 1 0. Transitions are also called edges. Clock Signals and Clocked FFs Clock Signals and Clocked FFs Clocked FFs change state on one or the other clock transitions. Some common characteristics: Clock inputs are labeled CLK, CK, or CP. A small triangle at the CLK input indicates that the input is activated with a PGT (see next page) A bubble and a triangle indicates that the CLK input is activated with a NGT (see next page) Control inputs have an effect on the output only at the active clock transition (NGT or PGT). These are also called synchronous control inputs. The control inputs get the FF outputs ready to change, but the change is not triggered until the CLK edge. Clock Signals and Clocked FFs Clock Signals and Clocked FFs Setup time (tS) is the minimum time interval before the active CLK transition that the control input must be kept at the proper level. Hold time (tH) is the time following the active transition of the CLK during which the control input must kept at the proper level. Clocked S-R Flip-Flop: Function The SET-RESET FF will change states at the positive going or negative going clock edge. Clocked S-R Flip-Flop: Waveform Clocked S-R Flip-Flop: Internal Circuitry See Next Page for the Edge Detector Clocked S-R Flip-Flop: Internal Circuitry Edge Detectors for (a) PGT and (b) NGT Clocked J-K Flip-Flop: Info Operates like the S-R FF. J is SET, K is RESET. Difference from the S-R FF: When J and K are both high, the output is toggled from whatever state it is into the opposite state – the toggle mode. May be PGT or NGT. Has the ability to do everything the S-R FF does, plus operating in the toggle mode. Clocked J-K Flip-Flop: Function Table PGT NGT Clocked J-K Flip-Flop: Internal Circuitry Clocked J-K Flip-Flop: Waveform Exercises (Clocked J-K FF) Exercises (Clocked NOR FF) Clocked D Flip-Flop: Info One data input. The output changes to the value of the input at either the positive going or negative going clock trigger. May be implemented with a J-K FF by tying the J input to the K input through an inverter. Useful for parallel data transfer. Clocked D Flip-Flop: Function Clocked D Flip-Flop: Parallel Data Transfer D Latch (Transparent Latch): Info One data input. The clock has been replaced by an enable line. The device is NOT edge triggered. The output follows the input only when EN is high. D Latch: Function D Latch: Waveform Asynchronous (Override) Inputs Inputs that depend on the clock are synchronous. Most clocked FFs have asynchronous inputs that do not depend on the clock. The labels PRE and CLR are used for asynchronous inputs. Active low asynchronous inputs will have a bar over the labels and inversion bubbles. If the asynchronous inputs are not used they will be tied to their inactive state. Note: We didn’t talk about this. The materials are included here for your information. Asynchronous Inputs: Function Note: We didn’t talk about this. The materials are included here for your information. IEEE/ANSI Symbols Note the differences in the representations below. PRE CLR Note: We didn’t talk about this. The materials are included here for your information. Flip-Flop Timing Considerations Important timing parameters: Setup and hold times Propagation delay – the time for a signal at the input to be shown at the output. Maximum clocking frequency – highest clock frequency that will give a reliable output. Clock pulse high and low times – minimum time that clock must high before going low, and low before gong high. Propagation delay may cause unpredictable outputs. Note: We didn’t talk about this. The materials are included here for your information. Flip-Flop Applications Examples of applications: Synchronization Synchronous Data Transfer Frequency Division Many FF applications are categorized as sequential, which means that the output follows a predetermined sequence of states. Application: Synchronization (1) Most systems are primarily synchronous in operation, where changes depend on the clock. Asynchronous and synchronous operations are often combined. The random nature of asynchronous inputs can result in unpredictable results. Example shown on the next page describes the problem and a solution using FF. Application: Synchronization (2) A Synchronization Problem: The synchronization problem solved by FF: Application: Detecting an Input Sequence FFs provide features that pure combinational logic gates do not. If an output is desired only when inputs change state in sequence, an arrangement similar to the following figure can be used. How about three inputs in sequence? Application: Synchronous Data Transfer (1) FFs are commonly used for storage and transfer of data in binary form. Groups of FFs used for storage are registers. Data transfers take place when data is moved between registers or FFs. Synchronous transfers take place at either PGT or NGT of the clock. Transferring the bits of a register simultaneously is a parallel transfer. Transferring the bits of a register one bit at a time is a serial transfer. Application: Parallel Data Transfer Parallel Transfer: Register contents are transferred simultaneously with a single clock cycle. Faster, the circuit is more complex. Application: Serial Data Transfer Serial Transfer: Register contents are transferred one bit at a time, with a clock pulse for each bit. Slower, the circuit is simpler. Application: Frequency Division & Counting (1) FFs are often used to divide a frequency. Application: Frequency Division & Counting (2) The same circuit is also acting as a binary counter. Application: Frequency Division & Counting (3) The counter has 23 = 8 different states. It is referred to as a MOD-8 counter, where the MOD number indicates the number of states in the counting sequence. In general, if N flip-flops are connected in a similar arrangement, the counter has 2N different states and so it is a MOD-2N counter. It can count up to 2N-1 before returning to its 0 state. State Transition Diagram Microcomputer Application