Clocks and Memory

advertisement

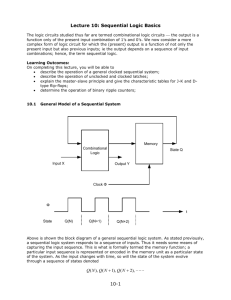

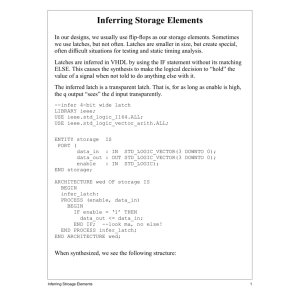

Computer Science 210 Computer Organization Clocks and Memory Elements Types of Logic Circuits • Combinational – – – – No memory Output depends only on inputs No state All circuits so far, ALU, etc. have been combinational • Sequential – Has memory – Memory holds state – Output depends on inputs and state Clocks • Clocks are used in sequential circuits to determine when an element should have its state updated. • A clock is a free running signal that emits pulses with precise pulse width and interval. • Clock cycle time is divided into two parts – When clock signal is high – When clock signal is low – The time of the changes are called edges (rising or falling) Clocks (cont.) • Edge triggered clocking – state changes occur on a clock edge (could specify rising edge or falling edge). Clocks (cont.) • General scenario is – Inputs to combinational circuit come from a state element (memory or register) – Output of combinational circuit goes into a state element – Clock cycle provides time for results of combinational component to settle. NAND and NOR Gates • A NAND B – NOT A AND B NAND Gate A • A NOR B – NOT A OR B B NOR Gate A B SR Latch Most of the time we have S=R=0. From this we can not determine Q. Check that S=R=Q=0 gives a “steady state”. Check that S=R=0, Q=1 gives a “steady state”. SR Latch Suppose we are in State 0: S=R=Q=0. Now suppose we change S to 1. Note that Q now becomes 1 (steady). If we now change S back to 0, Q remains 1. We are now in State 1: S=R=0, Q=1. So, from State 0, we can change to State 1, by setting S to 1 and then back to 0. SR Latch Suppose we are in State 1: S=R, Q=1. Now suppose we change R to 1. Note that Q now becomes 0 (steady). If we now change R back to 0, Q remains 0. We are now in State 0: S=R=Q=0. So, from State 1, we can change to State 0, by setting R to 1 and then back to 0. D Latch Here C is a clock line and D is the data line. Note that if the clock is at 0, both AND gates produce 0 (S=R=0); so the SR latch keeps whatever state it is in (independent of D). Now suppose D=1, and C becomes 1. The upper AND gate produces 0, and the lower AND gate produces 1 (S=1, R=0); this sets state to State 1 (same as D). When clock goes back to 0, state does not change. If D had been 1, state would be State 1 (same as D). So state changes to D when clock is at 1. D Flip-flop Here the first latch (master) gets its value from D when clock is high. At this point, the second latch has clock 0 so isn’t changing. When the clock pulse falls, the second latch gets its state from the output of the master latch. So state of the flip-flop changes on falling edge. Comments • Latches and flip-flops are memory elements. They have state that changes only on signal (clock signal). • Latches change state whenever clock is high (could be low). • Flip-flops are edge triggered. Enable Lines W To store new value, must have clock high and have the write enable line high. Building a Register Stores a multi-bit value Collection of D-latches are controlled by a common WE When WE = 1, n-bit value is written to the register Building Memory 22 x 3 Memory word select word WE input bits address write enable address decoder output bits