Example Questions in Chaps 4 and 5

advertisement

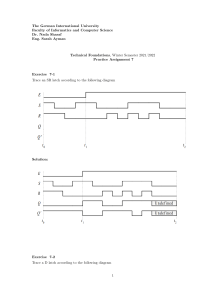

Problem 1 Problem 2 Problem 3 Problem 4 Problem 5 Figure 1 shows a sequential logic with 2-bit state elements (2 D-latches). In this figure, each of the 2-bit states is represented by (Q1 Q0). The next state (D1 D0) transition will be determined by the present (Q1 Q0) and a single-bit input X. The F1 function is defined as: next_state=(present_state*3+X+1)%4, where '%' denotes the modulo operation which takes the remainder of the division as the result of the operation). For example: if the present_state=(1 0)2=2, and X=1, the next state will be (2*3+1+1)%4=8%4=0=(0 0)2 2 D0D D C D latch Q D Q D latch _ C Q QQ0 _ Q C D1D F1 D C C D latch Q D Q D latch _ C Q QQ1 _ Q X Q0 Q1 D0 D1 Figure 1 1) Given the initial state (Q1 Q0) to be (0 1) and a sequence of synchronous input signals X to be 1, 0, 0, 1 (i.e., the transitions of input signals occur on the falling edge of each clock cycle, trace the logic of Q1, Q0, D1, D0 for 4 cycles. Use Figure 1 to trace the logic! 2) What is the function of D1 (in terms of Q1, Q0, and X)? 3) What is the function of D0?