Design for testability

advertisement

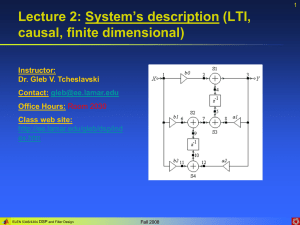

ELEN 468 Advanced Logic Design Lecture 24 Design for Testability ELEN 468 Lecture 24 1 Test Cost Test pattern generation Fault simulation Generation of fault sites information Test equipment Test process Test cost may overweight design cost ELEN 468 Lecture 24 2 Why Design for Testability? Testability is a design characteristic that influences various costs associated with testing It allows for Device status to be determined Isolation of faults Reduce test time and cost ELEN 468 Lecture 24 3 Controllability Ability to establish a specific signal value at each node by setting circuit’s inputs Circuits typically difficult to control: decoders, circuits with feedback, oscillators, clock generators … ELEN 468 Lecture 24 4 Observability Ability to determine the signal value at any node in a circuit by controlling the circuit’s inputs and observing its output ELEN 468 Lecture 24 5 Predictability Ability to obtain known output values in response to given input stimuli Factors affecting predictability Initial state of circuit Races Hazards …… ELEN 468 Lecture 24 6 Difficult Test Cases Sequential logic is more difficult to test than combinational logic Control logic is more difficult to test than data-path logic Random logic is more difficult to test than structured bus-oriented designs Asynchronous design is more difficult to test than synchronous design ELEN 468 Lecture 24 7 Quantify Testability Need approximate measure of: Difficulty of setting internal circuit lines to 0 or 1 by setting primary circuit inputs Difficulty of observing internal circuit lines by observing primary outputs Uses: Analysis of difficulty of testing internal circuit parts – redesign or add special test hardware Guidance for algorithms computing test patterns – avoid using hard-to-control lines Estimation of fault coverage Estimation of test vector length ELEN 468 Lecture 24 8 Types of Measures SCOAP – Sandia Controllability and Observability Analysis Program Combinational measures: CC0 – Difficulty of setting circuit line to logic 0 CC1 – Difficulty of setting circuit line to logic 1 CO – Difficulty of observing a circuit line Sequential measures – analogous: SC0 SC1 SO ELEN 468 Lecture 24 9 Range of SCOAP Measures Controllabilities – 1 (easiest) to infinity (hardest) Observabilities – 0 (easiest) to infinity (hardest) Combinational measures: Roughly proportional to # circuit lines that must be set to control or observe given line Sequential measures: Roughly proportional to # times a flip-flop must be clocked to control or observe given line ELEN 468 Lecture 24 10 Controllability Examples ELEN 468 Lecture 24 11 Observability Examples ELEN 468 Lecture 24 12 Goal of Design for Testability (DFT) Improve Controllability Observability Predictability ELEN 468 Lecture 24 13 Design and Test Trade-off Most DFT ( Design for Testability ) techniques need extra hardware, or modification to circuits that may affect performances DFT need to consider the cost trade-off between design and test ELEN 468 Lecture 24 14 DFT Methods DFT methods for digital circuits: Ad-hoc methods Structured methods: Scan Partial Scan Built-in self-test (BIST) Boundary scan ELEN 468 Lecture 24 15 Ad-Hoc DFT Methods Good design practices learnt through experience are used as guidelines: Avoid asynchronous (unclocked) feedback Make flip-flops initializable Avoid redundant gates Avoid large fanin gates Provide test control for difficult-to-control signals Avoid gated clocks Design reviews conducted by experts or design auditing tools Disadvantages of ad-hoc DFT methods: Experts and tools not always available Test generation is often manual with no guarantee of high fault coverage Design iterations may be necessary ELEN 468 Lecture 24 16 Scan Design Circuit is designed using pre-specified design rules Test structure (hardware) is added to the verified design: Add a test control (TC) primary input Replace flip-flops by scan flip-flops (SFF) and connect to form one or more shift registers in the test mode Make input/output of each scan shift register controllable/observable from PI/PO ELEN 468 Lecture 24 17 Scan Design Rules Use only clocked D-type of flip-flops for all state variables At least one PI pin must be available for test; more pins, if available, can be used All clocks must be controlled from PIs ELEN 468 Lecture 24 18 Correcting a Rule Violation All clocks must be controlled from PIs Comb. logic D1 Q Comb. logic FF D2 CK Comb. logic D1 D2 CK ELEN 468 Lecture 24 Q FF Comb. logic 19 Scan Storage Cell D Si N/T’ Clk Q, So SSC SSC D ELEN 468 Lecture 24 Q 20 Scan Flip-Flop (SFF) Master latch D N/T’ Slave latch Q Logic overhead Si MUX Q Clk D flip-flop ELEN 468 Lecture 24 21 Scan Methods C1 C2 C1 MUX C2 Si ELEN 468 Lecture 24 22 Boundary Scan MUX ELEN 468 Lecture 24 23 Integrated Serial Scan PI PO Combinational SFF logic SFF SCANOUT SFF Control SCANIN ELEN 468 Lecture 24 24