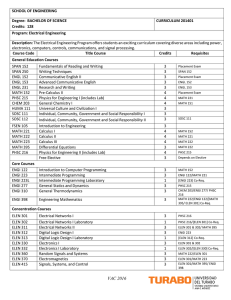

Built-in self-test

advertisement

ELEN 468 Advanced Logic Design Lecture 25 Built-in Self Test ELEN 468 Lecture 25 1 BIST ( Built-in Self Test ) PRPG: Pseudo Random Pattern Generator ORA: Output Response Analyzer CUT: Circuit Under Test Start PRPG PI CUT PO ORA Pass/fail ELEN 468 Lecture 25 2 BIST Motivation Useful for field test and diagnosis (less expensive than a local automatic test equipment) ELEN 468 Lecture 25 3 Benefits and Costs of BIST Level Design and test Fabri- Manuf. Maintenance Diagnosis Service and repair interruption cation Test test Chips +/- + - Boards +/- + - System +/- + - - - - + Cost increase - Cost saving +/- Cost increase may balance cost reduction ELEN 468 Lecture 25 4 Economics – BIST Costs Chip area overhead for: Test controller Hardware pattern generator Hardware response compacter Testing of BIST hardware Pin overhead – at least 1 pin needed to activate BIST operation Performance overhead – extra path delays Reliability reduction – due to increased area and complexity ELEN 468 Lecture 25 5 BIST Benefits Reduced testing and maintenance cost Lower test generation cost Reduced storage / maintenance of test patterns Simpler and less expensive ATE Can test many units in parallel Shorter test application times Can test at functional system speed ELEN 468 Lecture 25 6 BIST Types On-line BIST Concurrent Non-concurrent Off-line BIST Functional Structural ELEN 468 Lecture 25 7 BIST Architecture ELEN 468 Lecture 25 8 Pseudo-Random Pattern Generation through LFSR Linear Feedback Shift Register (LFSR) Produces patterns algorithmically – repeatable Has most of desirable random # properties Long sequences needed for good fault coverage ELEN 468 Lecture 25 9 Response Compaction Severe amounts of data in CUT response to LFSR patterns – example: Generate 5 million random patterns CUT has 200 outputs 5 million x 200 = 1 billion bits response Uneconomical to store and check all of these responses on chip Responses must be compacted ELEN 468 Lecture 25 10 LFSR for Response Compacter ELEN 468 Lecture 25 11 Signature Analysis Signature – any statistical circuit property distinguishing between bad and good circuits Aliasing – due to information loss, signatures of good and some bad machines match Signature analysis – compare good machine response into good machine signature. Actual signature generated during testing, and compared with good machine signature ELEN 468 Lecture 25 12 BILBO (Built-in Logic Block Observer) Four modes: 1. 2. 3. 4. Flip-flop LFSR pattern generator LFSR response compacter Scan chain for flip-flops ELEN 468 Lecture 25 13 Example of BILBO Combined functionality of D flip-flop, pattern generator, response compacter and scan chain ELEN 468 Lecture 25 14 BILBO Serial Scan Mode B1 B2 = “00” Dark lines show enabled data paths ELEN 468 Lecture 25 15 BILBO LFSR Pattern Generator Mode B1 B2 = “01” ELEN 468 Lecture 25 16 BILBO in D-FF (Normal) Mode B1 B2 = “10” ELEN 468 Lecture 25 17 BILBO in Response Compactor Mode B1 B2 = “11” ELEN 468 Lecture 25 18 Exercises 7 ELEN 468 Lecture 25 19 Problem 1 always @ ( … ) begin for ( j = 0; j < n; j = j + 1 ) begin a[j] = 0; for ( k = 0; k < j; k = k + 1 ) @ ( posedge clock ) a[j] = a[j] + x[k]; end end always @ ( … ) begin … a[0] = 0; for ( j = 0; j < n; j = j + 1 ) begin @ ( posedge clock ) a[j] = a[j-1] + x[j-1]; end end ELEN 468 Lecture 25 20 Problem 2 clock a x Flip-flop y b c Latch ELEN 468 Lecture 25 z 21 Problem 3.1 Reg b Reg a Reg c + + + ELEN 468 Lecture 25 22 Problem 3.2 Reg b Reg a Reg c + + + ELEN 468 Lecture 25 23