VHDL

advertisement

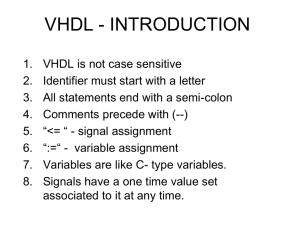

ELEN 468 Advanced Logic Design Lecture 19 VHDL ELEN 468 Lecture 19 1 Introduction VHDL VHSIC Hardware Description Language VHSIC Very High Speed Integrated Circuit ELEN 468 Lecture 19 2 Example -- eqcomp4 is a four bit equality comparator -- Entity declaration entity eqcomp4 is port ( a, b: in bit_vector( 3 downto 0 ); equals: out bit ); -- equal is active high end eqcomp4; -- Architecture body architecture dataflow of eqcomp4 is begin equals <= ‘1’ when ( a = b ) else ‘0’; end dataflow; ELEN 468 Lecture 19 3 Entity Declarations Describe I/O and parameterized values Port declaration Name Mode in out buffer: for internal feedback inout Data type Boolean, bit, bit_vector, integer, std_logic … ELEN 468 Lecture 19 4 Example of Entity Declaration library ieee; use ieee.std_logic_1164.all; entity add4 is port ( a, b: in std_logic_vector( 3 downto 0 ); ci: in std_logic; sum: out std_logic_vector( 3 downto 0 ); co: out std_logic ); end add4; ELEN 468 Lecture 19 5 Architecture Bodies Always associated with an entity declaration Description styles Behavioral Dataflow Structural ELEN 468 Lecture 19 6 Behavioral Descriptions library ieee; use ieee.std_logic_1164.all; entity eqcomp4 is port ( a, b: in std_logic_vector( 3 downto 0 ); equals: out std_logic ); end eqcomp4; architecture behavioral of eqcomp4 is begin comp: process ( a, b ) -- sensitivity list begin if a = b then equals <= ‘1’; else equals <= ‘0’; -- sequential assignment endif end process comp; end behavioral; ELEN 468 Lecture 19 7 Dataflow Descriptions library ieee; use ieee.std_logic_1164.all; entity eqcomp4 is port ( a, b: in std_logic_vector( 3 downto 0 ); equals: out std_logic ); end eqcomp4; architecture dataflow of eqcomp4 is begin equals <= ‘1’ when ( a = b ) else ‘0’; end dataflow; -- No process -- Concurrent assignment ELEN 468 Lecture 19 8 Structural Descriptions library ieee; use ieee.std_logic_1164.all; entity eqcomp4 is port ( a, b: in std_logic_vector( 3 downto 0 ); end eqcomp4; equals: out std_logic ); use work.gatespkg.all; architecture struct of eqcomp4 is signal x : std_logic_vector( 0 to 3); begin u0: xnor2 port map ( a(0), b(0), x(0) ); -- component instantiation u1: xnor2 port map ( a(1), b(1), x(1) ); u2: xnor2 port map ( a(2), b(2), x(2) ); u3: xnor2 port map ( a(3), b(3), x(3) ); u4: and4 port map ( x(0), x(1), x(2), x(3), equals ); end struct; ELEN 468 Lecture 19 9 Identifiers Made up of alphabetic, numeric, and/or underscore The first character must be a letter The last character cannot be an underscore Two underscores in succession are not allowed Uppercase and lowercase are equivalent ELEN 468 Lecture 19 10 Data Objects Constants Signals constant width: integer := 8; signal count: bit_vector( 3 downto 0); Similar to “wire” in Verilog Variables Only in processes and subprograms Usually applied as loop or tmp variable Files ELEN 468 Lecture 19 11 Data Types Scalar types Composite types ELEN 468 Lecture 19 12 Scalar Types Enumeration Integer Floating Physical ELEN 468 Lecture 19 13 Enumeration Types type states is ( idle, waiting, read, write ); signal current_state: states; type bit is ( ‘0’, ‘1’ ); type std_ulogic is ( ‘U’, -- Uninitialized ‘X’, ‘0’, ‘1’, ‘Z’, ‘W’, -- Weak unknown ‘L’, -- Weak 0 ‘H’, -- Weak 1 ‘-’, -- Don’t care ); ELEN 468 Lecture 19 14 Integer and Floating Types VHDL supports Integers from –(231-1) to (231-1) Floating number from –1E38 to 1E38 variable a: integer range –255 to 255; ELEN 468 Lecture 19 15 Physical Types type time is range –2147483647 to 2147483647 units fs; ps = 1000 fs; ns = 1000 ps; us = 1000 ns; ms = 1000 ns; sec = 1000 ms; min = 60 sec; hr = 60 min; end units; -- time is a predefined type -- physical types are mostly for simulations ELEN 468 Lecture 19 16 Composite Types Array Record type bit_vector is array ( natural range <> ) of bit); Has multiple elements of different types ELEN 468 Lecture 19 17 Two Dimensional Array type table8x4 is array ( 0 to 7, 0 to 3 ) of bit; constant exclusive_or: table8x4 := ( “000_0”, “001_1”, “010_1”, “011_0”, “100_1”, “101_0”, “110_0”, “111_1” ); ELEN 468 Lecture 19 18 Strongly Typed VHDL is a strongly typed language If a and b are integer variables, following assignment is not allowed a <= b + ‘1’; since ‘1’ is a bit, unless ‘+’ is overloaded ELEN 468 Lecture 19 19 Concurrent Statements Lie outside of a process Signal assignment Concurrent Selective (with-select-when) Conditional (when-else) Generate ELEN 468 Lecture 19 20 Concurrent Signal Assignment entity my_design is port ( mem_op, io_op: in bit; read, write: in bit; memr, memw: out bit; io_rd, io_wr: out bit ); end my_design; architecture control of my_design is begin memw <= mem_op and write; memr <= mem_op and read; io_wr <= io_op and write; io_rd <= io_op and read; end control ELEN 468 Lecture 19 21 Selective Signal Assignment entity mux is port ( a, b, c, d: in bit_vector( 3 downto 0 ); s: in bit_vector( 1 downto 0 ); x: out bit_vector( 3 downto 0 ) ); end mux; architecture archmux of mux is begin with s select x <= a when “00”, b when “01”, c when “10”, d when others; end archmux; ELEN 468 Lecture 19 22 Conditional Signal Assignment entity mux is port ( a, b, c, d: in bit_vector( 3 downto 0 ); s: in bit_vector( 1 downto 0 ); x: out bit_vector( 3 downto 0 ) ); end mux; architecture archmux of mux is begin x <= a when ( s = “00” ) else b when ( s = “01” ) else c when ( s = “10” ) else d; end archmux; ELEN 468 Lecture 19 23 Component Instantiation and Generate Statement architecture RTL of SHIFT is component DFF port ( rst, clk, d: in bit; q: out bit ); end component; signal T: bit_vector( 8 downto 0 ); begin T(8) <= SI; SO <= T(0); g0: for i in 7 downto 0 generate -- variable i is implicitly declared allbit: DFF port map ( rst=>rst, clk=>clk, d=>T(i+1), q=>T(i)); end generate; end RTL; ELEN 468 Lecture 19 24 Sequential Statements In a process, function or procedure if-then-else when-else ELEN 468 Lecture 19 25 if-then-else … if ( condition1 ) then x <= value1; elsif ( condition2 ) then x <= value2; else x <= value3; end if; ELEN 468 Lecture 19 26 case-when … architecture design of test_case is begin process ( address ) begin case address is when “001” => decode <= X”11”; -- X indicates hexadecimal when “111” => decode <= X”42”; when “010” => decode <= X”44”; when “101” => decode <= X”88”; when others => decode <= X”00”; end case; end process; end design; ELEN 468 Lecture 19 27 Loop … p0: process ( A ) variable sum, i : integer; begin sum := 0; loop1 : for i in 0 to 9 loop exit loop1 when A(i) > 20; next when A(i) > 10; sum := sum + A(i); end loop loop1 end process ELEN 468 Lecture 19 28 D Flip-Flop library ieee; use ieee.std_logic_1164.all; entity dff is port ( d, clk, rst: in std_logic; q: out std_logic ); end dff; architecture behavior of dff is begin process ( clk, rst ) begin if rst = ‘1’ then q <= ‘0’; elsif ( clk’event and clk = ‘1’ ) then q <= d; -- ‘event is an attribute end if; end process; end behavior ELEN 468 Lecture 19 29 wait-until library ieee; use ieee.std_logic_1164.all; entity dff is port ( d, clk, rst: in std_logic; q: out std_logic ); end dff; architecture behavior of dff is begin process ( clk, rst ) begin if rst = ‘1’ then q <= ‘0’; else wait until ( clk = ‘1’ ) q <= d; end if; end process; end behavior ELEN 468 Lecture 19 30 Functions function bl2bit ( a: BOOLEAN ) return BIT is begin if a then return ‘1’; else return ‘0’; end if end bl2bit; ELEN 468 Lecture 19 31 Using Functions entity full_add is port ( a, b, carry_in: in bit; sum, carry_out: out bit ); end full_add; architecture fall_add of full_add is function majority( a, b, c: bit ) return bit is begin return ( ( a and b ) or ( a and c ) or ( b and c ) ); end majority; begin sum <= a xor b xor carry_in; carry_out <= majority( a, b, carry_in ); end; ELEN 468 Lecture 19 32 Procedures procedure dff ( signal d: bit_vector; signal clk, rst: bit; signal q: out bit_vector ) is begin if rst = ‘1’ then q <= ( others => ‘0’ ); elsif clk’event and clk = ‘1’ then q <= d; end if; end procedure; ELEN 468 Lecture 19 33 Packages Similar to library A design unit whose type, component, function and other declarations can be visible to outside Consists of Package declaration Package body (optional) Made visible through “use” use library_name.package_name.item; use work.std_arith.all; Some vendors provide a default work library ELEN 468 Lecture 19 34 Declare Types in Package package STANDARD is type BOOLEAN is ( FALSE, TRUE ); type BIT is ( ‘0’, ‘1’ ); type INTEGER is range -2147483648 to +2147483647; … end STANDARD; ELEN 468 Lecture 19 35 Define Procedure in Package package myflop is procedure dff ( signal d: bit_vector; signal clk, rst: bit; signal q: out bit_vector ); end myflop; package body myflop is procedure dff ( signal d: bit_vector; signal clk, rst: bit; signal q: out bit_vector ) is begin if rst = ‘1’ then q <= ( others => ‘0’ ); elsif clk’event and clk = ‘1’ then q <= d; end if; end procedure; end myflop; ELEN 468 Lecture 19 36 Using Procedure entity flop8 is port ( clk, rst: in bit; data_in: in bit_vector( 7 downto 0 ); data: out bit_vector( 7 downto 0 ) ); end flop8; use work.myflop.all; architecture archflop8 of flop8 is begin dff( data_in, clk, rst, data ); end archflop8; ELEN 468 Lecture 19 37 Generics entity dff is generic ( size: integer := 2 ) port ( clk, rst: in bit; d: in bit_vector( size-1 downto 0 ); q: out bit_vector( size-1 downto 0 ) ); end dff; architecture behavior of dff is … end behavior … u1: dff generic map(8) port map( myclk, myrst, data, output ); … ELEN 468 Lecture 19 38