16-bit

Memory System

5-1

Address Bus (A0 – A19)

1M x 8

Data Bus ( D0 – D7)

Logical Memory Map.

Each location size is one byte

(Byte Addressable)

Address Bus (A0 – A19)

512K x 8 512K x 8

D0 – D7

Data Bus (D0 – D15)

D8 – D15

Logical Memory Map.

Each location size is one byte

(Byte Addressable)

Address Bus (A0 – A19)

512K x 8 512K x 8

D0 – D7

Data Bus (D0 – D15)

D8 – D15

EVEN addresses goes to bank 0

Bank 0

ODD addresses goes to bank 1

Bank 1

Logical Memory Map.

Each location size is one byte

(Byte Addressable)

Address Bus (A0 – A19) EVEN addresses goes to bank 0

Bank 0

ODD addresses goes to bank 1

Bank 1

512K x 8 512K x 8

D0 – D7

Data Bus (D0 – D15)

D8 – D15

MOV [1000], AX

DS:1000 = AL

DS:1001 = AH

AL AH

Logical Memory Map.

Each location size is one byte

(Byte Addressable)

Address Bus (A0 – A19) EVEN addresses goes to bank 0

Bank 0

ODD addresses goes to bank 1

Bank 1

512K x 8 512K x 8

D0 – D7

Data Bus (D0 – D15)

D8 – D15

MOV [1001], AX

DS:1001 = AL

DS:1002 = AH

AH

AL

Logical Memory Map.

Each location size is one byte

(Byte Addressable)

1

1

BHE'

0

0

0

1

A0

0

1

Function

Both banks are enabled for a

16-bit transfer

High bank enabled for an 8-bit transfer low bank enabled for an 8-bit transfer

No banks enabled

Designing Larger Memories

64M X 32 memory using

16M X 16 chips

5-9

Full mapping

Memory Mapping

5-10

Memory Mapping (cont’d)

Partial mapping

5-11

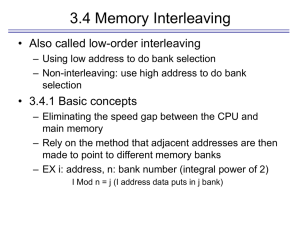

Interleaved Memory

• In our memory designs

– Block of contiguous memory addresses is mapped to a module

• One advantage

– Incremental expansion

• Disadvantage

– Successive accesses take more time

» Not possible to hide memory latency

• Interleaved memories

– Improve access performance

• Allow overlapped memory access

• Use multiple banks and access all banks simultaneously

– Addresses are spread over banks

» Not mapped to a single memory module

5-12

Interleaved Memory (cont’d)

5-13

Interleaved Memory (cont’d)

Interleaved memory allows pipelined access to memory

5-14

Interleaved Memory (cont’d)

• Number of banks

– M = memory access time in cycles

– To provide one word per cycle

• Number of banks

M

• Drawbacks of interleaved memory

– Involves complex design

• Example: Need MDR or MAR

– Reduced fault-tolerance

• One bank failure leads to failure of the whole memory

– Cannot be expanded incrementally

5-15

1. Static RAM (SRAM)

• Essentially uses flip-flops to store charge (transistor circuit)

• As long as power is present, transistors do not lose charge

(no refresh)

• Very fast (no sense circuitry to drive nor charge depletion)

• Complex construction

• Large bit circuit

• Expensive

• Used for Cache RAM because of speed and no need for large volume

5-16

Static RAM Structure

1

1 0 “NOT”

1

0 six transistors per bit

(flip flop)

0 1

0/1 = example

0

5-17

2. Dynamic RAM (DRAM)

• Bits stored as charge in capacitors

• Simpler construction

• Smaller per bit

• Less expensive

• Slower than SRAM

• Typical application is main memory

• Essentially analogue -- level of charge determines value

5-18

X

Dynamic RAM Structure

‘High’ Voltage at Y allows current to flow from X to Z or Z to X

Y

Z

+ one transistor and one capacitor per bit

5-19

SRAM v.s. DRAM

Static Random Access Memory

(SRAM)

Dynamic Random Access Memory

(DRAM)

Storage element

Advantages

Disadvantages

Applications

1.

Fast

2.

No refreshing operations

1.

Large silicon area

2.

expensive

High speed memory applications,

Such as cache

1.

High density and less expensive

1.

Slow

2.

Require refreshing operations

Main memories in computer systems

5-20

DRAM Organisation

• Two dimensional matrix

• Bits are accesses by:

– Accepting row and column addresses down the same multiplexed address

– First: Row address is presented and latched by ras signal

A[n:0]

– Next: column address is presented and latched by cas signal ras array of memory cells

Output register mux

Data out

5-21 cas

Typical 16 Mb DRAM (4M x 4)

RAS = Row Addr. Select

CAS = Column Addr. Select

WE = Write Enable

OE = Output Enable

2 k x 2 k = 4 M nybble

5-22

Accessing DRAMs

DRAM block diagram

Addr[7:0]

CAS

Column decoder

Storage Array

RAS

5-23

Accessing DRAMs

Address bus selection circuit

Row Address

Column Address

MUX To DRAM address decoder

CLK

IO/M

D

RAS

Q set

D Q

Q set

D Q

CAS set

5-24

Accessing DRAMs

Refreshing operations

— Because leakage current will destroy information stored on DRAM capacitors periodic refreshing operations are required for DRAM circuits

— During refreshing operation, DRAM circuit are not able to response processor’s request to perform read or write operations

— How to suspend memory operations?

— DRAM controllers are developed to take care DRAM refreshing operations

5-25

5-26