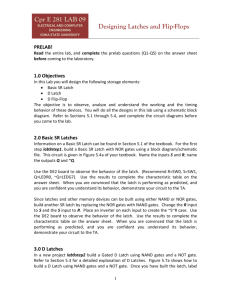

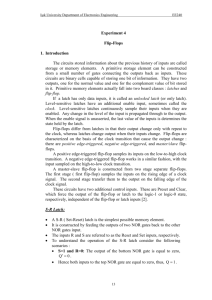

EENG 2710 Ch 6

advertisement

EENG 2710 Chapter 6 Introduction to Sequential Logic 1 Chapter 6 Homework Work on your project 2 Sequential Circuit • A digital circuit whose output depends not only on the present combination of input, but also on the history of the circuit. 3 Sequential Circuit Elements • Two basic types: – Latch – Flip-flop • The difference is the condition under which the stored bit changes. 4 SR Latch • The LATCH is a sequential circuit with two inputs (SET and RESET). • SET – an input that makes the device store a logic 1. • RESET – an input that makes the device store a logic 0. 5 SR Latch • Two complementary outputs (Q , Q ). • Outputs are always in opposite logic states. 6 Active HIGH or LOW Inputs • Latches can have either active HIGH or active LOW inputs. • The output of the LATCH, regardless of the input active level, is still defined as: SET : Q 1, Q 0 RESET : Q 0, Q 1 7 Active HIGH or LOW Inputs 8 NAND Latch Function Table Qt 1 Qt 1 0 0 1 1 Function Forbidden 0 1 1 0 SET 1 0 0 1 RESET 1 1 Qt Qt S R No Change 9 NAND Latch Reset to Set Transition 10 NAND Latch Reset to Set Transition 11 NAND Latch Set to Reset Transition 12 NAND Latch Reset to Set Transition 13 NOR Latch Function Table 14 NOR Latch Reset to Set Transition 15 NOR Latch Reset to Set Transition 16 NOR Latch Set to Reset Transition 17 NOR Latch Set to Reset Transition 18 Switch Bounce • The condition where the closure of a switch contact results in a mechanical bounce before the final contact is made. • In logic circuits, switch bounce causes several pulses when a switch is closed. – Can cause circuit to behave unpredictably. 19 Switch Bounce 20 Switch Debounce Circuit S 1, R 1 21 Gated SR Latch • The time when a latch is allowed to change state is regulated. • Change of state is regulated by a control signal called ENABLE. • Circuit is a NAND latch controlled by steering gates. 22 Latch ENABLE Input EN S R Qt+1 1 0 0 Qt 1 1 1 0 0 1 1 X 1 0 1 X 0 1 1 Qt Function No change 1 0 1 Reset Set Forbidden Inhibited 23 Gated D or Transparent Latch • A latch whose output follows its data input when its ENABLE input is active. • When ENABLE is inactive, the latch stores the data that was present when ENABLE was last active. 24 Gated D Latch Function Table 25 Flip-Flop Definition • A gated latch with a clock input. • The sequential circuit output changes when its CLOCK input detects an edge. • Edge-sensitive instead of level-sensitive. • Positive edge: The transition from logic ‘0’ to logic ‘1’ • Negative edge: The transition from logic ‘1’ to logic ‘0’ • Symbol is a triangle on the CLK (clock) input of a flipflop. 26 Positive Edge-Triggered D Flip-Flop 27 Edge Detector • A circuit that converts that active-edge of a CLOCK input into a brief active-level pulse. • Created using gate propagation delays. • Can be positive or negative edge. • The inverter in a below has 3 to 10ns propagation delay 28 Operation of Positive Edge D Flip-flop 29 VHDL – D Latch d_latch_vhdl.vhd -- D latch with active-HIGH level-sensitive enable ENTITY d_latch_vhdl IS PORT( d, ena : IN BIT; q : OUT BIT); END d_latch_vhdl; 30 VHDL – D Latch ARCHITECTURE a OF d_latch_vhdl IS BEGIN PROCESS ( d, ena) BEGIN IF ( ena = ‘1’) THEN q <= d; END IF; END PROCESS; END a; 31 JK Flip-Flop • Two inputs with no illegal input states. • With J and K both HIGH, the flip-flop toggles between opposite logic states with each applied clock pulse. 32 Negative Edge-Triggered JK Flip-Flop 33 Toggle Action 34 Toggle Applications • Used to divide an input frequency in half. • By cascading toggling flip-flops, a counter is created. 35 Synchronous And Asynchronous Circuits • Synchronous circuits have sequential elements whose outputs change at the same time. • Asynchronous circuits have sequential elements whose outputs change at different times. 36 Synchronous and Asynchronous Inputs • Synchronous inputs of a flip-flop only affect the output on the active clock edge. • Asynchronous inputs of a flip-flop change the output immediately. • Asynchronous inputs override synchronous inputs. 37 3-Bit Synchronous Circuits 38 Flip-Flop Asynchronous Inputs • Preset: – An asynchronous set function, usually designated as PRE • Clear: – An asynchronous reset function, usually designated as CLR • Both Preset and Clear usually have LOW input active levels. 39 Flip-Flop Asynchronous Inputs 40 3-Bit Synchronous Circuits With Asynchronous Reset • An asynchronous input used to set a sequential circuit to a known initial state. • Usually a RESET tied to the CLR inputs of all flip-flops. • When activated, the output of the sequential circuit goes LOW. 41 Disadvantages of Asynchronous Circuits • Difficult to analyze operations. • Intermediate states that are not part of the desired design may be generated. 42 JK Flip-Flop Asynchronous Inputs Function Table CLR 43 Unused Preset and Clear Inputs • Disable by connecting to a logic HIGH (for active-LOW inputs). • In Quartus II the asynchronous inputs of all flip-flop primitives are set to a default level of HIGH. 44 T (Toggle) Flip-Flop • Output toggles on each applied clock pulse when a synchronous input is active. • Synchronous input is designated as ‘T’. 45 T Flip-Flop Function Table CLK T Qt+1 Function ↑ 0 Qt No change ↑ 1 Qt Toggle 0 X Qt Inhibited 1 X Qt Inhibited ↓ X Qt Inhibited 46 D Flip-Flop Configured for Toggle Function 47