Mealy Level-to-Pulse Converter

advertisement

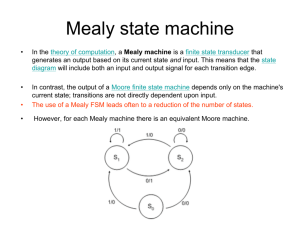

Experiment 7 蔡政翰, Jeng-Han Tsai jhtsai@ntnu.edu.tw Department of Applied Electronic Technology Finite State Machines Two Types of FSMs Moore FSM Inputs X 0 ,X1,...Xn Comb. Logic Next State n D Flip-flop Q S+ Comb. Logic Outputs Yk = Fk (S) clk n Present state S Mealy FSM Direct combinational path! Outputs Inputs X 0 ,X1,...Xn Comb. Logic n Comb. Logic D Flip-flop Q S+ clk n 2 Yk = Fk (S,X 0 ...Xn ) Moore FSM A sequential circuit (inputs, current state) (output, next state) State Diagram State Table 3 Moore FSM D=JQ'+K'Q A(t 1) JA K A B(t 1) JB K B State equation for A and B: A(t 1) BA ( Bx) A AB AB Ax B(t 1) xB ( A x)B Bx ABx ABx 4 Moore FSM //Moore model FSM (See Fig.5.19) module Moore_Model_Fig_5_19 ( output [1:0] y_out, input x_in, clock, reset); reg [1:0] state; parameter S0 = 2’b00, S1 = 2’b01, S2 = 2’b10, S3 = 2’b11; always @ (posedge clk, negedge reset) if (reset == 0) state <= S0; // Initialize to state S0 else case (state) S0: if(~x_in) state <= S1; else state <= S0; S1: if(x_in) state <= S2; else state <= S3; S2: if(~x_in) state <= S3; else state <= S2; S3: if(~x_in) state <= S0; else state <= S3; endcase assign y_out = state; // Output of flip-flops endmodule 5 Mealy FSM A sequential circuit (inputs, current state) (output, next state) State Diagram State Table 6 Mealy FSM State equations A(t+1) = A(t)x(t) + B(t)x(t) B(t+1) = A'(t)x(t) The output equation y(t) = (A(t)+B(t))x'(t) 7 Mealy FSM //Mealy FSM zero detector (See Fig.5.16) module Mealy_Zero_Detector( output reg y_out, input x_in, clock, reset); reg [1:0] state, next_state; parameter S0 = 2’b00, S1 = 2’b01, S2 = 2’b10, S3 = 2’b11; always @ (posedge clk, negedge reset) if (reset == 0) state <= S0; else state <= next_state; always @ (state, x_in) // Form the next state case (state) S0: if(x_in) next_state = S1; else next_state = S0; S1: if(x_in) next_state = S3; else next_state = S0; S2: if(~x_in) next_state = S0; else next_state = S2; S3: if(x_in) next_state = S2; else next_state = S0; endcase always @ (state, x_in) // Form the output case (state) S0: y_out = 0; S1, S2, S3: y_out = ~x_in; endcase 8 endmodule Example Level-to-Pulse A level-to-pulse converter produces a single-cycle pulse each time its input goes high it’s a synchronous rising edge detector L Whenever input L goes from low to high Level to pulse converter P … output P produces a single pulse, one clock period wide clk State Transition Diagrams is a useful FSM representation and design aid “if L=1 at the clock edge, then jump to state 01” L=1 L=0 00 Low input, Waiting for rise P=0 L=1 01 Edge detected P=1 L=0 “if L=0 at the clock edge, then stay in state 00” L=0 9 Binary values states 11 11 High input, Waiting for fall P=0 P=0 L=1 This is the output that results from this state. (Moore or Mealy) Example Logic Derivation for a Moore FSM converted to a state transition table L=1 00 Low input, Waiting for rise P=0 L=0 L=1 01 Edge detected P=1 L=0 11 High input, Waiting for fall P=0 L=1 L=0 Current state S0 S1 0 0 0 0 1 0 1 0 1 1 1 1 Combinational logic may be derived by Karnaugh maps S1 S 0 L 0 1 S1 S 0 L 0 1 S1 for S 1 00 01 11 10 0 0 0 X 0 1 1 X for S 0 00 01 11 10 0 0 0 X 1 1 1 X L Next n State D Flip-flop Q S Comb. Logic 0 L 0 1 0 1 0 1 fo r Present state S P 10 P S0 0 0 1 0 X 1 1 0 Comb. Logic cl k S1 LS0 S + L n Next state S 0 S1 0 0 1 0 0 0 1 1 0 0 1 1 In P S1S0 P Out P 0 0 1 1 0 0 Example Moore Level-to-Pulse Converter S1 LS0 S0 L L P S 1S 0 S0 D clk 1 Q S0 Q D Q S Q 11 S1 P Mealy Level-to-Pulse Converter Since outputs are determined by state and inputs, Mealy FSMs may need fewer states than Moore FSM implementations When L = 1 and S = 0, output P is asserted immediately and until the state transition occurs (or L changes) Output transitions immediately. State transitions at the clock edge. 1 L 2 P Clock State L=1/ P=1 0 Input is low L=0/P=0 1 Input is high After the transition to S = 1 and as long as L remains at 1, output P is asserted L=1/ P=0 L=0/ P=0 Pres. State In Next State Out S L S P 0 0 0 0 0 1 1 1 1 0 0 0 1 1 1 0 12 Mealy Level-to-Pulse Converter Mealy FSM circuit implementation P S L CLK D Q Q S FSM’s state simply remembers the previous value of L Circuit benefits from the Mealy FSM’s implicit single-cycle assertion of outputs during state transitions 13 Trade-Offs between Moore/Mealy Differences Moore outputs are based on state only Mealy outputs are based on state and input Mealy outputs generally occur one cycle earlier than a Moore L L P P Clock Clock State[0] State Compared to a Moore FSM, a Mealy FSM might... Be more difficult to conceptualize and design Have fewer states 14 Practice Department of Applied Electronic Technology Practice 1 Please think about level-to-pulse converter, and give a reason why the number of the states cannot be reduced to two states in Moore FSM. (回答於實驗報告內) 請完成Page11與Page13兩種型態的Verilog語法,不限撰寫層次; 並以波形模擬、DE2實驗板驗證 DE2 Board Pin: Input: L (SW0) Output: P (LEDR0) , State (HEX0) 參考投影片中的準位脈衝轉換電路,試設計另一形態之脈衝轉換電路,波形如下: Moore或Mealy FSM擇一。 波形模擬、DE2實驗板驗證。 DE2 Board Pin: Input: L (SW0) Output: P (LEDR0) , State (HEX0) 16 The END 17