2015_6_23_Huang_DRC_slides.pptx

advertisement

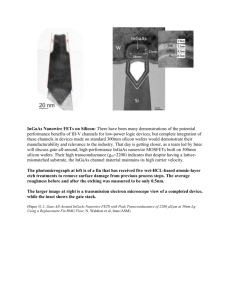

12 nm-Gate-Length UltrathinBody InGaAs/InAs MOSFETs with 8.3∙105 ION/IOFF Cheng-Ying Huang1, Prateek Choudhary1, Sanghoon Lee1, Stephan Kraemer2, Varistha Chobpattana2, Brain Thibeault1, William Mitchell1, Susanne Stemmer2, Arthur Gossard1,2, and Mark Rodwell1 1Electrical and Computer Engineering, University of California, Santa Barbara 2Materials Department, University of California, Santa Barbara Device Research Conference 2015 Late News Columbus, OH III-V FETs at sub-10-nm nodes? • III-V channels: low electron effective mass, high velocity, high mobility higher Ion at lower VDD reducing switching power • III-V FETs have high leakage current because: Low bandgap larger band-to band tunneling (BTBT) leakage High permittivity worse electrostatics, large subthreshold leakage • Ioff<100 nA/µm (High performance) and Ioff<100 pA/µm (Low power) • Question: Can III-V MOSFETs scale to sub-10-nm nodes? Logic industry node Physical gate length (nm) 16/14 20 10 17 7 14 5 12 Ref: 2013 ITRS Roadmap 2 Record high performance III-V FETs 1 Lg = 25 nm 3.0 10 I = 500 A/ m at I =100 nA/ m on off 0 10 and V =0.5V 2.5 D -1 10 SS~ 72 mV/dec. 2.0 -2 10 SS~ 77 mV/dec. -3 1.5 10 -4 10 1.0 -5 10 0.5 -6 10 -7 10 -0.3 -0.2 -0.1 0.0 0.1 0.2 0.3 0.4 0.50.0 Lg~25 nm gm (mS/m) Current Density (mA/m) S. Lee et al., VLSI 2014 N+ S/D Vertical Spacer Ion (mA/m) Gate Bias (V) 0.50 VDS = 0.5 V 0.45 Ioff=100 nA/m 0.40 0.35 0.30 0.25 0.20 0.15 0.10 10 S. Lee, VLSI 2014 J. Lin, IEDM 2013 T. Kim, IEDM 2013 Intel, IEDM 2009 J. Gu, IEDM 2012 D. Kim, IEDM 2012 100 Gate Length (nm) 3 Record low leakage III-V FETs Lg-30nm Lg-30nm C. Y. Huang et al., IEDM 2014 • • • Minimum Ioff~ 60 pA/μm at VD=0.5 V for Lg-30 nm Recessed InP shows 100:1 smaller Ioff compared to InGaAs spacers BTBT leakage is completely removed sidewall leakage dominates Ioff 4 UCSB Gate Last Process Flow HSQ Channel Ch. Barrier Substrate Barrier Substrate MBE grown device epilayer Pattern dummy gate Source/drain recess etch HSQ N+ S/D Barrier Substrate MOCVD source/drain regrowth Ti/Pd/Au ZrO2 Ni Ni N+ S/D Ch. Barrier Substrate Ch. N+ S/D Ch. Barrier Substrate Lift-off gate metal Isolation Strip dummy gate Digital etch Deposit ALD dielectric FGA anneal N+ S/D Ch. Barrier Substrate Deposit S/D contacts 5 TEM images of Lg~12 nm devices Lg~12nm N+InGaAs Cross-setion N+InP ~ 8nm Ni InP spacer Top View InAlAs Barrier tch~ 2.5 nm (1.5/1 nm InGaAs/InAs) 6 ID-VG and ID-VD curves of 12nm Lg FETs Lg-12nm 1.0 2.4 VDS = 0.1 to 0.7 V, 2.0 0.2 V increment 1.6 0.6 1.2 0.4 0.8 0.2 0.0 10 Ioff~1.3 nA/μm V = 0.1 to 0.7 V 1 10 -1 10 -2 10 -3 10 -4 10 -5 10 -6 10 -7 10 -8 1.5 0.2 V increment SS ~ 107.5 mV at VDS=0.5 V SS ~ 98.6 mV at VDS=0.1 V -0.2 0.0 0.4 0.0 0.2 0.4 VGS (V) VGS = -0.2 V to 1.2 V DS 0.2 0.4 V (V) 0.6 0.8 ID (mA/m) ID, |IG| (mA/m) 10 0 1.0 gm (mS/m) ID (mA/m) 0.8 0.6 0.8 0.0 Ion~1.1 mA/μm 0.2 V increment Ron = 302 Ohm-m at VGS = 1.0 V Ion/Ioff > 8.3∙105 0.5 0.0 0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 VDS (V) 7 3.5 2.5nm InAs+12nm InGaAs spacer 4.5nm InGaAs+graded InP spacer This work Peak Gm (mS/m) 3.0 2.5 2.0 1.5 1.0 0.5 0.0 VDS = 0.5 V 0.01 0.1 Gate length (m) 1 On Resistance (Ohm-m) On-state performance 1250 1000 750 2.5nm InAs+12 nm InGaAs spacer at VGS=0.7V 4.5nm InGaAs+graded InP spacer at VGS=1V This work at VGS=1V 500 Ron at zero Lg ~220 Ohm.m ~260 Ohm.m ~262 Ohm.m 250 0 0.00 0.05 0.10 0.15 0.20 0.25 Gate length (m) • Slightly higher Gm for a 2.5 nm composite channel than a 4.5 nm InGaAs channel larger gate capacitance. • A 2.5nm InAs channel with a 12 nm InGaAs spacer shows highest Gm high indium content channel is desirable for UTB III-V FETs. • InP spacers increase parasitic RS/D to ~260 Ω∙μm InP spacers need further optimization. 8 140 400 VDS=0.1 V, 2.5nm InAs VDS=0.5 V, 2.5nm InAs VDS=0.1 V, 4.5nm InGaAs 120 VDS=0.5 V, 4.5nm InGaAs VDS=0.1 V, This work 100 VDS=0.5 V, This work 80 60 0.01 0.1 Gate length (m) 1 300 DIBL (mV/V) Subthreshold Swing (mV/dec) Subthreshold characteristics 2.5nm InAs+12nm InGaAs spacer 4.5nm InGaAs+graded InP spacer This work Vth at 1 A/m 200 100 0 0.01 0.1 Gate length (m) • A 2.5nm InAs channel with a 12 nm InGaAs spacer shows the lowest SS and DIBL because of the best electrostatics. • A 5 nm un-doped InP spacer with the atop 8 nm linearly doping-graded InP have shorter effective gate length as compared to 12 nm un-doped InGaAs spacers worse electrostatics. • SS~107 mV/dec. and DIBL~260 mV/V for 12 nm devices FinFETs will cure this. 9 Ion and Ioff versus Lg 700 Ion (A/m) 600 IOFF, MIN (nA/m) 2.5nm InAs+12nm InGaAs spacer 4.5nm InGaAs+graded InP spacer This work 500 400 300 200 VDS = 0.5 V 100 0 Ioff = 100 nA/m 0 20 40 60 80 100 Gate length (nm) 120 10 3 10 2 10 1 10 0 10 -1 10 -2 10 -3 2.5nm InAs+12nm InGaAs spacer 4.5nm InGaAs+graded InP spacer This work VDS = 0.5 V 10 100 Gate length (nm) 1000 • High In% content channels are required to improve Ion, but Ioff is relatively large (~10 nA/µm). • InGaAs channels with recessed InP source/drain spacers are required for low leakage FETs. • A clear tradeoff between on-off performance. 10 6 1.5 4 1.0 2 0.5 0.4 0.6 0 1.0 0.8 ) 0.2 -2 0.0 0.0 VGS (V) 500 Mobility~ 250 cm2/V∙s 12 2.0 W/L= 25m/21 m 2 Cox = 4.2 F/cm 6 5 EOT= 0.8 nm 1.5 4 1.0 3 2 0.5 1 2.5 nm InAs 5.0 nm InAs 0.0 -0.2 0.0 0.2 0.4 Gate Bias (V) 0 0.6 800 2 eff (cm /s-V) 2 Mobility (cm /Vs) 7 1000 300 200 100 1.5/1 nm InGaAs/InAs 0 Freq: 200kHz 1200 VDS = 25 mV to 50 mV 400 2.5 Carrier Density (/cm ) 2 1.5/1 nm InGaAs/InAs 2.0 12 Cacc (F/cm ) 8 Carrier density (10 cm Freq: 200 kHz EOT~ 0.9~1 nm 2.5 0.2 V increment InAs channel x 10 10 VDS = 0.1 to 0.7 V 2 This work 3.0 Gate Capacitance (F/cm2) Mobility extraction at Lg-25 µm long channel FETs 0 1 2 3 4 5 6 -2 Carrier density (cm ) 600 400 Mobility~ 280 cm2/V∙s 200 0 0 m*, RS/D more important! 2.5 nm InAs 5.0 nm InAs 1 2 3 4 5 6 Carrier Density (/cm2) 7 12 x 10 11 Summary •We demonstrated a 12nm-Lg ultrathin body III-V MOSFET with well-balanced on-off performance. (Ion/Ioff> 8.3·105) •The 12nm-Lg FET shows Gm~1.8 mS/µm and SS~107 mS/dec., and minimum Ioff~ 1.3 nA/µm. •High indium content channel is required to improve on-state current. (High performance logic) •Thin channels, InGaAs channels, and recessed InP source/drain spacers are the key design features for very low leakage III-V MOSFETs. (Low Power Logic) •III-V MOSFETs are scalable to sub-10-nm technology nodes. 12 Acknowledgment Thanks for your attention! Questions? • This research was supported by the SRC Non-classical CMOS Research Center (Task 1437.009) and GLOBALFOUNDRIES(Task 2540.001). • A portion of this work was done in the UCSB nanofabrication facility, part of NSF funded NNIN network. • This work was partially supported by the MRSEC Program of the National Science Foundation under Award No. DMR 1121053. cyhuang@ece.ucsb.edu (backup slides follow) 10 -2 10 S. Lee et al., VLSI 2014 Dot : Reverse Sweep Solid: Forward Sweep Lg = 1 m 10 1 10 0 10 -1 10 -2 10 -3 -3 10 -4 10 -5 10 -6 10 -7 10 SSmin~ 61 mV/dec. (at V DS = 0.1 V) SSmin ~ 63 mV/dec. 10-4 (at V = 0.5 V) -8 DS 10 10 -0.1 0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 -5 2 Current Density (mA/m) -1 |Gate Leakage| (A/cm ) Record low subthreshold swing Gate Bias (V) Achieved SS~ 61 mV/dec. Superior high-k dielectrics on III-V channels. Dielectrics from Gift Chobpattana, Stemmer group, UCSB. 15 Why InAs channel is better… • Electron scattering with oxide traps inside conduction band • Electrons in high In% content channel have less scattering with oxide traps. N. Taoka et al., Trans. Electron Devices. 13, 456 (2011) N. Taoka et al., IEEE IEDM 2011, 610. J. Robertson et al., J. Appl. Phys. 117, 112806 (2015) J. Robertson, Appl. Phys. Lett 94, 152104 (2009) Ni/Au 50 nm N+InGaAs 1.2 13 nm U.I.D InP 4.5 nm InGaAs Back Barrier 5 nm InP spacer 13 nm InP spacer 0.02 0.04 0.06 0.08 0.10 500 400 300 100 0 5 nm InP spacer, RS/D~199 m 13 nm InP spacer, RS/D~364 m 0.02 0.04 0.06 10 nm nm N+InP N+InP 10 13 nm U.I.D InP 3 nm 1.0 Gate length (m) 200 ZrO2 0.08 Gate length (m) 0.10 InGaAs Channel 0.5 0.0 Fermi level -0.5 -1.0 N+InGaAs Source N+InP 0.0 50 nm N+InGaAs 10 nm N+InP 0.8 0.4 Ti/Pd/Au Ni/Au Barrier 1.6 600 Ron (m) Ti/Pd/Au VDS = 0.5 V Spacer 2.0 Energy (eV) Peak gm (mS/m) InP spacer thickness: on-state -1.5 -2.0 0 20 40 60 80 Distance to source contact (nm) Thicker InP spacer increases Ron, and degrades Gm Thinner spacer is desired at source to reduce RS/D. 17 Doping-graded InP spacer 1 Lg-30 nm, 30Å ZrO2 5 nm UID InP 13 nm UID InP Doping graded InP ~199 ~364 ~270 -0.2 0.0 0.2 1.6 gm (mS/m) Ron at zero Lg (Ω∙μm) 2.4 2.0 ID, |IG| (mA/m) 10 0 VDS = 0.1 to 0.7 V 10 -1 0.2 V increment 10 -2 10 -3 ID 10 -4 10 -5 10 -6 |IG| 10 -7 10 -8 10 -9 10 1.2 0.8 0.4 0.4 0.6 0.0 VGS (V) Doping-graded InP spacer reduces parasitic source/drain resistance and improves Gm. Gate leakage limits Ioff~300 pA/μm. 18