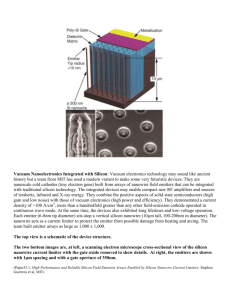

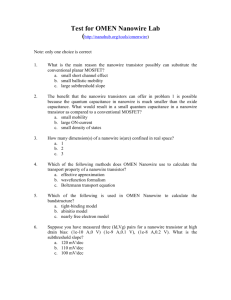

InGaAs Nanowire FETs on Silicon: There have been many

advertisement

InGaAs Nanowire FETs on Silicon: There have been many demonstrations of the potential performance benefits of III-V channels for low-power logic devices, but complete integration of these channels in devices made on standard 300mm silicon wafers would demonstrate their manufacturability and relevance to the industry. That day is getting closer, as a team led by Imec will discuss gate-all-around, high-performance InGaAs nanowire MOSFETs built on 300mm silicon wafers. Their high transconductance (gm=2200) indicates that despite having a latticemismatched substrate, the InGaAs channel material maintains its high carrier velocity. The photomicrograph at left is of a fin that has received five wet-HCL-based atomic-layer etch treatments to remove surface damage from previous process steps. The average roughness before and after the etching was measured to be only 0.5nm. The larger image at right is a transmission electron microscope view of a completed device, while the inset shows the gate stack. (Paper 31.1, Gate-All-Around InGaAs Nanowire FETS with Peak Transconductance of 2200 μS/μm at 50nm Lg Using a Replacement Fin RMG Flow; N. Waldron et al, Imec/ASM)