80GHz Modulator Designs

advertisement

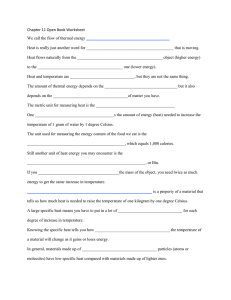

80GHz Modulator Designs Ian Harrison School of Electrical and Electronic Engineering University of Nottingham UK Work done at Department of ECE University of California, Santa Barbara USA Special thanks PK, Zak, Mattias for fabrication of circuits and devices Miguel for advice Paidi and Navin for cricket discussions Mark Rodwell for useful discussion and use of infrastructure Harrison@ece.ucsb.edu 805-893-8044, 805-893-3262 fax Introduction • Concentrate on more recent work • Thermal Modelling • Modulator work – design issues – Simulation results Design Specifications • Two types of optical modulator – LiNb03 Mach Zehnder -Interference • Split beam into 2, induce 0 or 180 phase shift • Large driving voltage eg 10GBits 5Vpp – Electroabsorption • Quantum confined stark effect • Smaller driving voltage eg 10GBits 3Vpp EA modulator 2V , 50 Ohm input Output should be matched E=0 Attn • Design specifications E≠0 E=0 E≠0 λ How do we get speed improvement • Switching speed limited by output capacitance C.V I Design Specifications set ΔV and RL sets I Formula simplistic insight Reduce C by decreasing AC Increase in J since I fixed J limited by Kirk Effect Increase in J increase dissipated power density Kirk effect and switching time Above Jkirk massive increase in base charge Base push out (Field Screening) J Kirk (Vcb )4vsat 2 TC AC V TC AE Vce 4vsat Wide emitter, narrow base mesa Rb limits the emitter width MAX VCE Predicts straight line J • (mA/m) 3.5 3 Vsat=3.5 105cms-1 2.5 2 1.5 0.6 0.8 1 1.2 1.4 V (V) CE 1.6 1.8 Why is thermal management important? • As J increases so does the power density. This will lead to an increase in the temperature. TC JKirk Le Å mAμm-2 μm 3000 1.0 81 2000 2.3 34 1500 4.1 19 1000 9.8 8.6 V=2V 80mA For VCE=1V PD=10.6mWμm-3 For VCE=1V PD=98mWμm-3!! Thermal Modeling of HBT (1) • 3D Finite Element using Ansys 5.7 • K (Thermal conductivity) depends temperature • K depends on doping 300 kT k300 T n • For GaAs heavily doped GaAs 65% less than undoped GaAs • Unknown for InP or InGaAs use GaAs dependency Material K300 n K300(exp) Refs InP 0.68 1.42 0.68-0.877 1 InGaAs 0.048 1.375 0.048-0.061 2 Au 3.17 - Large uncertainty in values 3 J.C.Brice in “Properties of Indium phosphide” eds S Adachi and J.Brice pubs INSPEC London p20-21 S Adachi in “Properties of Latticed –Matched and strained Indium Gallium Arsenide” ed P Bhattacharya pubs INSPEC London p34-39 “CRC Materials science and engineering handbook”, 2nd edition ,eds J.F Shackelford,A.Alexander, and J.S Park, pubs CRC press, Boca Raton, p270 Layout used for simulation validation Need simplified model for simulation Actual device reduce simulation time and storage requirements Ignore base pad collector interconnect •2 orthogonal symmetry lines •Simulate only ¼ device Layer structure Emitter Base Collector Setback Grade Drift Subcollector Etchstop Substrate 0.04μm n+ InGaAs 0.12 μm n- InP 0.03 μm p+ InGaAs Polyimide for passivation Very low K ignore In thermal analysis After M. Dahlstrom 4 0.02 μm InGaAs 0.024 μm Grade 0.156 μm InP 1.5 7.2 3.5 4 2 1 14 0.7 0.050 μm n+ InGaAs 0.200 μm n+ InP 500 μm Fe: InP 2.5 0.25 0.1 102.5 Simulated ¼ Device 4 0.5 102.5 500 Validation of Model 40 Caused by Low K of InGaAs Max T in Collector Temperature Rise (K) 35 center Edge 30 25 20 15 10 5 SC ES C B E E Metal 0 -0.2 0 0.2 0.4 0.6 0.8 1 1.2 Distance from substrate (m) Ave Tj (Base-Emitter) =26.20°C Measured Tj=26°C Good agreement. Advice Limit InGaAs Increase size of emitter arm Effect of decreasing collector thickness Assumptions Devices thermally isolated Device structure identical to validation structure Choose Le For J=JKirk We=0.5um Perfect switching waveform 50% duty cycle Increase in ISC possible failure mechanism ( Major failure problem in GaAs HBT’s) Temperature of one device approximately double when circuit is not switching 6mA 360 12 350 10 340 8 330 6 320 4 310 2 0 300 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 Collector Thickness (m) Length of Emitter (m) Collector temperature always higher than Tj (ΔTMax-ΔTj)>30°C ) Temperature (K) Observations Temperature increases rapidly for thin collectors (ΔTmax =60°C for TC=1000Å) V=0.3V Analysis of 40,80,160 Gbit/s devices • To obtain speed inprovements require to scale other device . parameters Speed (Gbit/s) 40 80 160 Collector Thickness (Å) 3000 2000 1000 Base Sheet resistance () 750 700 700 Base contact resistance (-m2) 150 20 10 Base Thickness (Å) 400 300 250 Base Mesa width ( m) 3 1.6 0.4 Current Density (mA/m2) 1 2.3 9.8 Emitter. Junction Width ( m) 1 0.8 0.2 Emitter Parasitic resistivity (-m2) 50 20 5 Emitter Length ( m) 6 3.3 3.2 Predicted MS-DFF (GHz) 62 125 237 Ft (GHz) 170 260 500 Fmax (GHz) 170 440 1000 Tj (K) 7.5 14 28 TMax (K) 10 20 49 TMax (No Etch Stop layer) (K) 7.5 13 21 Device parameters after Rodwell et al V=0.3V 6mA Reduction of parasitic CBC Conservative 1.5x bit rate When not switching values will double Thermal Analysis using ADS R network easily solved Using ADS • For simulations need a model that can be solved by ADS so that thermal and circuit simulations can be coupled. • • • • Thermal generation current source Thermal resistance resistors Thermal capacity capacitors (If static not needed) Temperature variation of thermal conductivity not modelled because resistors do not depend on current (This restriction could be lifted) Coupled Circuit-Thermal modelling • How do the advance device models do it? – Device at one temperature – Devices thermally isolated and described by a single resistance – Thermal circuit hidden from user • How do we want to do it – – – Access to thermal circuit β only slightly temperature dependent Large change in VBE(ON) VBE T •Β is the band gap shrinkage factor Not usually given but optical measurements on band gap ( Optical values must be used with caution ) 0.0004 for both InP and InGaAs Value used in model Ambient T Temperate rise Power dissipated in the device Thermal Resistance My model Can we measure Rth (Method of Lui et al ) 0.010 Ramp IB for different VCE Measure VBE and IC IC.i 0.008 0.006 0.004 0.002 0.000 0.48 Depends on current density 0.54 VBE 5000 4000 0.52 Large uncertainty in values. Fitting regression curves helps to reduce error RT VBE RT VCE I C 0.50 3000 2000 1000 2 3 4 PAve 5 6 -3 x 10 An alternative method for finding RT IC fixed , sweep VB Obtain RT (Pave) Changes in VC larger more accurate RT measured at lower Pave Thermal instability possible Need to be careful on the VB range 5000 2.5 Ic= 6mA,6mA Ic=12mA,12mA From gradient RT 4000 RT 2 3000 1.5 1 dVBE RT I C dVCE 1 0.5 0.74 RoT= 1945 0.76 0.78 0.8 0.82 2000 1000 0 Ic= 6mA,6mA Ic=12mA,12mA 0.01 0.02 PIn 0.03 Comparison of the two methods Emitter Mask 12 x 0.7 mesa width 1.7 “New method” Classic Method 5000 Linear interpolation. RT 3000 3000 2000 2000 1000 0 0.005 0.01 PAve 0.015 0.02 Empirical Curve fit RT 4000 3000 2000 0.005 0.01 PAve 1000 0 0.01 0.02 0.03 PIn 5000 1000 0 RoT= 1945 4000 RT 4000 5000 0.015 0.02 Classic method badly affected by the 4145 resolution. Better measurements at very high power. Often leads to device failures Problems with every fourth measurement of 4145 in “new” method Need to compare the two methods using the 4155 Which model to estimate Rth • Finite elements clearly shows diffusion of heat along the collector under the base contacts. • Rth should depend on base mesa size Model 1 Models flow of heat under base Thermal circuit complex Model 2 Thermal circuit simple Over estimates RT Both Models Both will underestimate RT at high powers Experimental results Model 2 Mesa Width Length Model 1 RT(C/W) 1.7 2.1 2.7 4 5500 5100 6200 12 1800 Use Model 2 1800 Thermal resistance calculations • Thermal resistance of layers can be estimated from the thermal conductivity if no heat spreading is assumed. • The emitter interconnect acts as a thermal link • The thermal resistance of the substrate is estimate by solving the 3D heat flow problem using separable variables technique. This is the same method Lui et al used to calculate RT of single and multifinger HBT power transistors.† Length Mesa Width RT(C/W) 1.7 2.1 2.7 Theory 4 5500 5100 6200 5700 12 1800 1800 2071 After M. Dahlstrom Spreadsheet: ThermalCalc.xls Stability of single BJT’s (Intro) 0.010 • • • Well known problem solved by ballasting with emitter or base resistance. Known to be a problem in power amplifiers. May argue, incorrectly, that in digital circuits this is not a problem because we are driving the circuits with a constant current source. Need to know how large we can make the emitters before “hot spots” form and current “hogging” becomes an issue. 0.008 IC.i • 0.006 X 0.004 0.002 0.000 0.48 0.50 0.52 0.54 VBE If the transistor base is being driven with a constant voltage. The collector current will increase until it gets to point X. Any further increase in base voltage will cause an infinite increase in the collector current resulting in physical damage to the device. Single Emitter Stability VC Max qI C RE kT I C RT (q k ) Caused by the increase in RT when device size is reduced. Uncertainty in Re Maximum VC for different IC. Emitter Length (Mask) =10m 2.4 0 3.4 3.2 Max 2.8 2.6 3.6 VC (V) VMax (V) C Stability curves against emitter length for const J 3.2 Caused by the reduction of Re with length 3 -2 JC= 2 mAm JC= 3 mAm-2 5 10 15 Emitter Length (Mask) (m) Optimum operating point Theory Experiment J =1 5mAμm-2 3 2.8 20 2.6 0 0.01 0.02 0.03 Collector Current (A) ρE=60Ω from DC measurements Hot spot formation (not finished) Device broken into sections Thermal model of substrate Base electrical resistance Need to do 1. Simulate DC measurements 2. Compare with measurements Thermal resistance of the emitter connection Modulator design (Matching) Passive simple high bias current Passive All active circuits Bias current lower need to prevent saturation Resistive feedback No flexibility Zo=1/gm Feedback Zo=1/(gmβ) but additional EF more ringing Resistive Feedback RC Feedback Feedback β<1 Effect of current source design on output Current switch (only one half) Vo Vm Capacitive coupling to Control line reduces output resistance Vi RiseI 1.556E11 FallI 2.161E11 RiseO 3.366E11 FallO 8.172E11 RiseI 1.476E11 2.5 RiseO 3.577E11 FallO 6.014E11 2.5 Common Reference 2.0 1.5 Different Reference 2.0 Vo 1.5 1.0 1.0 Voltage Voltage FallI 2.012E11 0.5 0.5 0.0 0.0 -0.5 -0.5 Vm -1.0 Vi -1.5 -5 0 -1.0 -1.5 5 10 15 20 Time (ps) 25 30 35 40 -5 0 5 10 15 20 Time (ps) Use resistor:- inefficient power use, but simple 25 30 35 40 Output stage options Performance depends on the quality of the ground Bias generated by diode Miller effect increases output cap 1.5 Ideal Vsrc Output Voltage 1.0 With diode base 0.5 0.0 -0.5 -1.0 -1.5 -5 0 5 10 15 20 time, psec 25 30 35 40 Current designs • 2 and 3 stage amplifiers • Cascode and simple output 3 stage cascode output 80GBit/s 160GBit/s 1.5 1.5 1.0 Output Voltage Output Voltage 1.0 0.5 0.0 -0.5 -1.0 0.5 0.0 -0.5 -1.0 -1.5 -5 0 5 10 15 20 time, psec 25 30 35 40 -1.5 -2 0 2 4 6 8 10 12 14 16 18 20 time, psec Simulations show that 160GBit is just possible with 1500A collector. What to do in the future • • • • Fabricate and test the current design Design amplifiers with output voltage Simulate with self heating Investigate the more advanced BJT models Conclusion • 160 Gbits Modulator has been designed • Electro -thermal model has been developed which can be simulated using ADS What would I change if I could rewind the clock Gone in the clean room.