Electronics for a Telemetric Brain

Electrode Array System

by

Jan Mal'sek

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Engineering in Electrical Engineering and Computer Science

At the Massachusetts Institute of Technology

May 14, 2002

©2002 Massachusetts Institute of Technology. All rights reserved.

Author

ience

Department of Electria Tngineering and Compu

May 14, 2002

Certified by

Professor Ian W. Hunter

Professor of Mechanical Engineering and Professor of BioEngineering

Thesis Supervisor

Accepted by

Arthur C. Smith

Chairman, Department Committee on Graduate Theses

1MASSACHUSETTS INSTITUTE

OF TECHNOLOGY

JUL 3 1 2002

LIBRARIES

2

Electronics for a Telemetric Brain Electrode Array System

by

Jan Malisek

Submitted to the Department of Electrical Engineering and Computer Science

May 14, 2002

in partial fulfillment of the requirements for the degree of

Master of Engineering in Electrical Engineering and Computer Science

Abstract

The Telemetric Electrode Array System (TEAS) is a surgically implantable device for

studying neural activity in the brain. An eight-by-eight array of needles collects intracortical neural signals for the electronics system to process and wirelessly transfer to an

external recording system; the waveforms can then be analyzed to provide insight about

information processing in the brain. We have designed an analog front end that amplifies

the microvolt level signals before they are digitized with 12 bits of resolution at 31 kHz

per channel. A digital subsection performs peak detection on the sixty-four channels to

compress data before sending them over a Bluetooth-based radio link at 725 kbit per

second. The individual sections of the system have been designed and tested, but a fully

integrated and implantable version has not been implemented due to time constraints.

Thesis Supervisor: Ian W. Hunter

Title: Professor of Mechanical Engineering and Professor of BioEngineering

3

Acknowledgements

I am grateful to the other members of the TEAS team, without whom a project of this

magnitude could not be undertaken. In particular, Johann Burgert was a great teammate

for designing the electronics and a good sport for letting me do the digital section, which

is obviously so much cooler than the analog electronics and wireless link. Tim Fofonoff

and Bobby Dyer contributed pictures and diagrams to this paper, and they generally

contributed to the entertaining atmosphere in lab. They also built the actual electrode

array (with help from Colette Wiseman and Marie-Maude de Denus Baillangeon). A

bunch of Canadians (Martin Labrecque, Fedor Danilenko, and Thor Bjarnason) helped

get the Bluetooth module up to speed and worked on the wireless charging system. The

Brown University people (Nicho Hatsopoulos, Misha Serruya, and John Donoghue) made

our lives difficult by giving us the specifications we needed to achieve, but they provided

ample support (including seats during the 10-hour surgery in which they stood and

implanted our thing). John Ankcorn and the ORnet people at LCS were very helpful,

especially given that they were not involved in the project. I'd also like to thank the

people who proofread and gave me feedback on this document, especially Johann, Peter

Madden, Candice Kamachi, and Sylvain Martel. And, of, course, I'd like to thank

Sylvain and Ian Hunter for making it possible for me to work on such an exciting project.

4

Contents

Abstract ...............................................................................................................................

3

Acknow ledgem ents......................................................................................................

4

Contents ..............................................................................................................................

5

List of Figures .....................................................................................................................

7

List of Tables ......................................................................................................................

8

1. Introduction....................................................................................................................

9

2. TEA S System Overview ..............................................................................................

13

The Electrode Array...................................................................................................

13

Flexible PCB .................................................................................................................

15

Electronics System .....................................................................................................

18

Analog Electronics................................................................................................

18

Bluetooth W ireless Com m unication M odule.........................................................

20

D igital Electronics ...............................................................................................

21

Pow er System ............................................................................................................

22

3. D igital Electronics D esign .......................................................................................

24

H igh-Level D esign Choices.......................................................................................

24

The H igh-Speed Processor A lternative..................................................................

24

The Parallel H ardw are A lternative ........................................................................

26

Compression Considerations ...............................................................................

27

Breaking Up the D igital Section................................................................................

29

The Program m able Logic System ..............................................................................

32

Choosing Components, Part 1: Programmable Logic Device Selection ...............

32

Choosing Components, Part 2: Transmit Buffer SRAM and Ring Buffer SRAM... 34

AD C Interface.......................................................................................................

35

Spike D etection System .........................................................................................

40

Transm it Buffer Control ........................................................................................

47

Unifying the Programmable Logic Modules: the Global Counter........................

49

The M icrocontroller ..................................................................................................

FPGA Configuration.................................................................................................

5

51

52

4. Prototypes and Results.............................................................................................

56

December 2001 Array Implant .................................................................................

56

D igital P rototyp e ...........................................................................................................

63

The Rest of TEA S ......................................................................................................

69

5 . C on clu sion ...................................................................................................................

71

R eferen ces .........................................................................................................................

75

Appendix A: VHDL Code .............................................................................................

77

Appendix Al: Spike Detection System VHDL Source: ringbuf.vhdl .......................

77

Appendix A2: Transmit Buffer Control VHDL Source: bigbuf.vhdl.......................

86

Appendix A3: ADC Serial Interface Input Control VHDL Source: serin.vhd.......... 89

Appendix A4: ADC Serial Interface Output Control VHDL Source: serout.vhd ........ 91

Appendix A5: Global Counter VHDL Source: cntr.vhd ..........................................

93

Appendix A6: TEAS Integration VHDL Source: teas.vhd........................................

94

Appendix B: Microcontroller Code to Configure FPGA...............................................

97

Appendix C: Java Source for FPGA Configuration File Compression..........................

102

Appendix C l: readbin.java .........................................................................................

102

Appendix C2: FileIO .java...........................................................................................

104

Appendix C3: BadFilenameException.java................................................................

106

Appendix Dl: BGA ZIF Socket Pinout..........................................................................

107

6

List of Figures

Figure 1: A Macaque monkey's skull is not much bigger than a computer mouse. ......... 10

Figure 2: Example 32-sample neural signals from existing tethered system, sampled at 20

kH z ............................................................................................................................

Figure 3: Major TEAS components, broken up by location of implantation. ..............

11

13

Figure 4: Electrode array after being machined from titanium block (photos by Tim

F o fono ff ) ..................................................................................................................

14

Figure 5: Electrode array assembly steps (drawing by Bobby Dyer and Tim Fofonoft). 15

Figure 6: Flexible printed circuit layout. .......................................................................

16

Figure 7: Flexible PCB detail around electrode array footprint. ..................................

16

Figure 8: Flexible PCB and 80-pin connector. The electrode array is soldered into the

holes on the left side of the PCB, which has laser cuts between traces to make it

more flex ib le.............................................................................................................

17

Figure 9: Electronics system block diagram. The analog section consists of 64 amplifiers

and 8 ADCs; the digital section, made up of an FPGA, two SRAMs, and a

microcontroller, processes the data from the ADCs and sends captured neural

waveforms to the Bluetooth wireless interface......................................................

18

Figure 10: Single channel of analog amplifier.............................................................

19

Figure 11: Digital electronics block diagram ................................................................

22

Figure 12: Abstraction and hierarchy in the TEAS electronics design.........................

30

Figure 13: The FPGA is one of the largest components in the design. ........................

34

Figure 14: ADC interface timing diagram for reading one sample. .............................

36

Figure 15: ADC interface timing for reading a sample every 16 clock cycles.............

36

Figure 16: Initial, highly parallel ADC interface block diagram..................................

37

Figure 17: Final ADC interface block diagram . ............................................................

39

Figure 18: Prestore, threshold, and poststore on a typical neural spike waveform. ......... 41

Figure 19: Spike detection system SRAM organization...................................................

42

Figure 20: STATUS variable bit descriptions. ...........................................................

43

Figure 21: Spike detection system state diagram.........................................................

46

7

Figure 22: Timing of data transfer between spike detection and transmit buffer SRAMs.

...................................................................................................................................

48

Figure 23: The 33-bit global counter. ............................................................................

49

Figure 24: FPGA passive serial (PS) configuration circuit. .........................................

53

Figure 25: FPGA passive serial (PS) configuration timing diagram. ............................

54

Figure 27: Adapter module for December 2001 implant (photo by Bobby Dyer). The

right end connects to the flexible PCB; the black Omnetics connectors are on the

left. ............................................................................................................................

57

Figure 28: Test electrode array for December 2001 implant (photo by Tim Fofonoff). .. 58

Figure 29: Surgeons attempt to permanently deform flexible PCB to conform to skull.. 59

Figure 30: The flexible PCB is tacked down to the skull with an acrylic adhesive before

the electrode array is inserted in the brain. ...........................................................

60

Figure 31: The electrode array, about to be inserted into the brain with a pneumatic

insertion too l. ............................................................................................................

61

Figure 32: The entire assembly is covered with an acrylic adhesive.............................

62

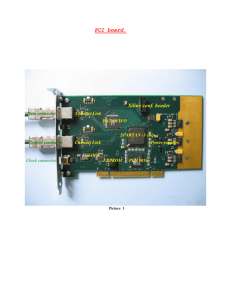

Figure 33: Component placement on the digital prototype. The PCB and component

outlines are show n actual size...............................................................................

64

Figure 34: Layout of top layer of digital prototype PCB...............................................

65

Figure 35: Layout of bottom layer of digital prototype PCB........................................

66

Figure 36: The fully assembled digital prototype..........................................................

67

Figure 37: Logic analyzer screen shot showing ADC serial clock and eight serial control

signals staggered by 2 clock cycles. ....................................................................

68

Figure 38: The digital prototype is not ready for implanting, yet..................................

69

Figure 39: Neural simulator circuits used to test amplifier circuit. ..............................

70

Figure 40: BG A ZIF socket pinout.................................................................................

107

List of Tables

Table 1: Power budget for TEAS electronics, assuming a 3.0 V power supply........... 23

8

1. Introduction

For the past decade, neurophysiologists have studied the brain using multichannel electrode arrays inserted directly into the brain. The small size of the electrodes

allows researchers to observe the electrical behavior of very small clusters of neurons and

possibly the activities of individual neurons.

Because of this high resolution, the

electrode arrays could potentially be used in human-machine interfaces that connect

directly to the brain. The notion of a brain-machine interface is not new, and even noninvasive attempts based on electroencephalograph (EEG) readings have yielded limited

successI; however, such non-invasive techniques generally measure the low-frequency

aggregate activity of large regions of the brain and thus do not provide the

communication bandwidth necessary for a practical interface 2 . Studies with existing

electrode arrays have indicated that only a few dozen electrode waveforms are sufficient

for prediction of a monkey's arm motion 3 , and the arrays could theoretically have

hundreds or even thousands of electrodes. Human-machine interfaces based on such

arrays would have the advantage of not requiring conscious thought, thus presenting

users with the ultimate in usability: operating a brain-interfaced device would be no

different from operating one's limbs. One of the first practical applications could indeed

involve electronically bypassing injured spinal cords to restore muscle control in

paraplegics.

Much neurological research is still necessary before the ultimate goal of a

practical brain-machine interface is realized.

An important step in advancing that

research is to develop better equipment and experimental processes. Current electrode

arrays require substantial support electronics outside of the skull for amplifying and

recording neural waveforms 4 . The external electronics must be tethered to the Macaque

monkeys on which experiments are typically performed; the monkeys must then be

restrained to prevent disconnection from the data acquisition system (and to keep the

monkeys from chewing through the cables). Because there is a direct, physical link from

the inside of the skull to the outside system, some wire or connector must protrude

through the skin, creating a potential for infection in the monkey.

The goal of the Telemetric Electrode Array System (TEAS) 5 is to create a

9

completely implantable, wireless system that will solve the problems with current,

tethered electrode arrays. The system will be used by Brown University neuroscientists,

who also specified most of the necessary design parameters. All electronics must fit

within a 50 mm x 50 mm x 10 mm case that will be implanted outside the skull but under

the skin. Figure 1 shows that the back of the monkey's skull, where the electronics will

be located, is about as large as the back of a computer mouse. A flexible printed circuit

will connect a custom, 64-electrode array to the electronics.

A battery and wireless

charging system can be implanted in the abdomen of the monkey and thus do not

contribute to the size of the main acquisition and control electronics on the skull.

To limit development time and cost, a primary initial requirement for the

electronics system was that it had to be made using only commercial, off-the-shelf

(COTS) components. This requirement, together with the small size requirement, has

had a substantial impact on the design and on the problems encountered.

A very

preliminary high-level design was made to determine the general types of components

required, and then a substantial amount of time was spent searching for the smallest

Figure 1: A Macaque monkey's skull is not much bigger than a computer mouse.

10

available components with the desired specifications. The final design was then crafted

around the components we could obtain. The implant would certainly be substantially

smaller if everything were built into a custom integrated circuit, but the current TEAS

design should fit within the available space limit.

The neural signals that TEAS must measure are the microvolt outputs of

individual neurons.

The electrode array is inserted in the general area of the motor

cortex, but there is no control over the final position of the electrode tips relative to

individual neurons.

The tips therefore pick up the signals of whichever neurons are

closest, and some electrodes will pick up good signals while others will not. A wellpositioned electrode should pick up signals that are about 100 pV peak-to-peak. Monkey

neurons fire approximately 1.5 ms spikes at 10-300 Hz 4 . A few sample spikes taken by

the existing data acquisition system are shown in Figure 2. The voltage typically drops

60

50

40

30

20

10

0 0

-20-30-40-50

0.0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

Time (ms)

Figure 2: Example 32-sample neural signals from existing tethered system, sampled at 20 kHz.

11

quickly, then rises above the idle level, and then returns more slowly to the starting

voltage. The voltage is roughly constant between spikes, and the details of the inactive

portion of the neural signal are not interesting to the TEAS users.

For the system to be useful, the TEAS electronics must digitize the analog neural

signals with twelve bits of resolution; the end users also want a minimum sampling rate

of 30 kHz. Therefore, transmitting just the raw data for all 64 channels, without any

communication protocol overhead, would require a 23 Mbps wireless connection.

Fortunately, the Brown scientists are interested only in the timing and shapes of the

approximately 1.5-ms-long neural spikes discussed above. Since the average spiking rate

is low, transmitting only the spikes reduces the bandwidth requirements by a factor of

fifty and makes the bandwidth requirement a more reasonable 500 kbps, again not

including any communications overhead. However, the electronics in the implant must

then perform some form of triggering and present a more complicated user interface that

allows the user to set the threshold and other peak detection parameters.

The TEAS electronics system will thus essentially be a 64-channel, wireless

oscilloscope that must be small enough to implant in a small monkey's head.

The

conflicting "64-channel" and "small, but with off-the-shelf components" requirements

made the design especially difficult. A large portion of the area on the final printed

circuit board will be taken up by amplifier circuits that are replicated 64 times since the

neural signals are too weak to multiplex without amplifying them first. Running 64

channels also complicates the digital portion of the system, which must perform peak

detection on 64 independent channels. The rest of this document will describe the details

of the TEAS electronics system design, present preliminary results, and indicate the

current status and future direction of the project.

12

2. TEAS System Overview

The entire TEAS system is a large project that does not involve electronics alone,

and it is therefore being designed and built by many members of the TEAS team; even

the electronics work is large enough of a task that it is being done by two individuals.

Before jumping into the digital electronics section, it is necessary to briefly describe all

the parts of the system and how they are interconnected.

A block diagram of the four major components of TEAS, broken up by location

of implantation within the test subject, is shown in Figure 3. The square, eight-by-eight

electrode array is inserted into the motor cortex of the brain. Most of the electronics

reside in the main unit implanted on the head. The electronics are mounted to the outside

of the skull, and they are connected to the array on the inside through a flexible printed

circuit board that contains sixty-four thin traces. The cable must be flexible enough to

allow the electrode array to move independently of the rest of the electronics and stay

implanted in the brain, which moves within the skull. The only electronics not on the

skull are the battery and wireless charging system, which can be implanted in the

abdomen of the monkey.

64-ELECTRODE

ARRAY

MOUNTED

ELECTRONICS

ECYTEMIC

SYSTE M

FLEXIBLE PCB

---

BATTERY AND

CHARGING

SYSTEM

Figure 3: Major TEAS components, broken up by location of implantation.

The Electrode Array

The electrode array 6 is a critical part of TEAS because it is the physical interface

between the electronics and the brain.

While designing and building the array is

primarily a mechanical engineering challenge undertaken by other members of the TEAS

team, some understanding of the array is important to the appreciation of the entire TEAS

project.

Furthermore, the electrodes are particularly significant to the electronics

designers because they are effectively electronic components.

13

Because the array is

connected to the electronics using flexible printed circuit board technology, a

combination of mechanical and electrical engineering techniques is necessary to achieve

the effective brain-electrode and electrode-electronics interfaces that are crucial to the

success of TEAS.

The electrode array is an 8 x 8 array of 1-mm-long electrodes that are 80 Am wide

and spaced 508 Am apart. Each electrode is electrically insulated except at its platinumcoated tip, which serves as the electrical contact point to the brain. The array is cut out of

Figure 4: Electrode array after being machined from titanium block (photos by Tim Fofonoff).

a solid piece of titanium using wire electrical discharge machining (wire EDM). Two

cutting passes are made with a 90-degree rotation between passes, resulting in electrodes

with a square cross-section, as shown in Figure 4. The electrodes are then coated with

gold and secured to a polyimide substrate before being cut off from the titanium base,

again using wire EDM. At this point, the electrodes are electrically isolated but held in

position by the polyimide.

The array is then soldered to a flexible PCB (described

below), which provides additional rigidity and electrical contacts to individual electrodes.

The entire assembly is then coated in parylene, a biocompatible insulator. The parylene

is removed only from the tips of the electrodes, which are then coated in platinum to

14

provide optimal neural reception. The array assembly is summarized in Figure 5.

Electrical Discharge Machine

(EDM) the array

Coat array with

gold strike

Solder array to flex-PCB

Remove electrodes

from base by EDM

Mount array

in substrate

-m1"m 010ir

Coat assembly with parylene

Solder connector

to flex-PCB

Create flexible Printed

Circuit Board (flex-PCB)

Create holes in polyimide

substrate and cut to size

P-M

Laser ablate the electrode tips

0

-10Coat electrode tips with platinum

6

Figure 5: Electrode array assembly steps (drawing by Bobby Dyer and Tim Fofonoff ).

Flexible PCB

The flexible printed circuit board (PCB) connecting the array to the electronics is

crucial not only for its obvious purpose of making the necessary connection, but because

it is part of the overall system design that makes TEAS superior to current research

equipment. Existing arrays use individual wires that must be painstakingly soldered onto

individual array electrodes, making the arrays costly to manufacture. With the flex PCB,

all traces are neatly packaged and the whole array can be mounted as a single component.

The current arrays have been mounted as through-hole components, with the backs of the

electrodes sticking through holes in the flex PCB on one side and getting soldered on the

other side. However, surface-mounting techniques similar to those used for chip-scale

electronic component packages are also being investigated by the electrode array

designers.

The wires connecting an electrode array to an external system must be very

flexible because a brain can move within a skull. Some of that movement is simply due

to the head moving around, but a large component of the motion comes from the whole

brain expanding and contracting with the animal's pulse. To make the PCB as flexible as

possible, the substrate was laser cut between traces. The traces were designed to be as

15

22.9 mm

I-

i

56.3 mm

Figure 6: Flexible printed circuit layout.

Figure 7: Flexible PCB detail around electrode array footprint.

small as possible while maintaining high manufacturing yield. The current version has

16

50 jm traces with 25 jim of the PCB substrate material on each side. A scale drawing of

the current flexible PCB is shown in Figure 6. Because the flex-PCB is only one-sided,

the trace routing is very tight, and the array footprint has various pad shapes to maximize

the soldering area for each electrode. A close-up view of the flexible PCB layout at the

array mounting point is shown in Figure 7.

Figure 8: Flexible PCB and 80-pin connector. The electrode array is soldered into the holes on the

left side of the PCB, which has laser cuts between traces to make it more flexible.

An important component of the flexible PCB module is a small, high-density

connector that will allow the flexible PCB to connect to the rigid PCB carrying most of

the electronics. A Molex7 connector pair8 (male part: 53794; female part: 54037) that is

only 1.15 mm high when connect is used. Unfortunately, the connector series is available

only in 60- and 80-pin versions. The lack of a 64-pin connector was common to many

17

manufacturers and connector lines, so the 80-pin Molex connectors represented the best

off-the-shelf solution. The connector and a completed flexible PCB are shown in Figure

8.

Electronics System

There are three main sections to the TEAS electronics: an analog front end that

does the necessary signal amplification and analog-to-digital conversion, a digital section

that performs peak detection and other processing, and a wireless communication module

(Figure 9)9.

This breakdown allowed simultaneous and independent design of the

different sections by different members of the design team. The interfaces between the

sections are dependent on the two sections they connect, but the digital system, which

connects to the other sections, is very flexible, allowing late modification to the interface.

Furthermore, the interface components of the analog and communications modules were

determined very early in the overall TEAS design.

4kx 16SRAM

64 RING BUFFERS

EIGHT

8-CHANNEL

2M x 8 SRAM

TRANSMIT FIFO

BUFFER

FPGA

16-BIT

MICROCONTROLLER

64 AMPLIFIERS

BLUETOOTH

Figure 9: Electronics system block diagram. The analog section consists of 64 amplifiers and 8

ADCs; the digital section, made up of an FPGA, two SRAMs, and a microcontroller, processes the

data from the ADCs and sends captured neural waveforms to the Bluetooth wireless interface.

Analog Electronics

The analog electronics is the interface between the brain and the rest of the

electronics.

The analog system provides the digital section with a simple, digital

18

interface that isolates the digital section from many of the difficulties of working in the

brain. Because the 64 inputs to the analog section are so weak, any form of multiplexing

prior to amplification isn't an option; therefore, the analog section contains 64 copies of

the same circuit. The size of the single amplifier circuit thus has a tremendous impact on

the overall size of the implant; the current analog design takes up approximately half of

the area taken up the entire electronics system. Power consumption considerations in the

individual amplifier circuits are also important because any increases in power

consumption are multiplied by a factor of 64.

The inputs to the analog section are the microvolt-level signals picked up by the

electrode array.

The peak-to-peak voltage on these signals is approximately 100

microvolts, requiring a gain of approximately five thousand to get to a 0.5 V peak-topeak voltage that is a minimum for the analog-to-digital converter.

The required

bandwidth, on the order of 10 kHz, puts the gain-bandwidth product at approximately 50

Mhz, well out of range of any low-power, single-stage amplifier. To simplify the power

system, we also decided on single-supply op-amps. Since the input signals can go both

positive and negative, a 1.5 V reference voltage is derived from the 3.0 V reference

voltage of the analog to digital converters. Figure 10 shows the final design for a single

channel of the analog circuit.

Besides amplifying the signal, the circuit also

3V

INPUT FROM

ELECTRODE

3V

+

.

-STAGE 1

G = 60

AIN

_

TO DIGITAL

3Va

FSUBSYSTEM

VREF

STAGE 2

G =70

3V

+

REFERENCE

ELECTRODE

1.5V

Figure 10: Single channel of analog amplifier.

performs RC high-pass filtering above approximately 200 Hz and low-pass, antialiasing

19

filtering below 15 kHz using the gain-bandwidth limitation of the op-amps. Two opamps are available in each package, so there are seven components per amplifier (five

resistors, one capacitor, and the op-amps). Even with this minimal circuit, the number of

components for the 64 amplifiers alone is 448 components.

Even with the smallest,

0201-size surface-mount components, which occupy approximately 1 mm x 1mm, the

analog circuitry consumes substantial space (approximately 30 mm x 30 mm for the

component footprints alone), and it is primarily for this reason that a more complex

amplifier and filter cannot be considered.

The 64 amplified signals are fed into eight separate 8-channel analog-to-digital

converters (ADCs). The ADCs thus provide multiplexing as well as the interface to the

digital section. For the implant to be useful, the Brown researchers required a minimum

of 12-bit sampling, and the 30 kHz minimum sampling requirement makes the minimum

aggregate sampling rate for each ADC 240 kHz. This sampling rate is low enough that

the ADC can be a very low power device, and the data rate is low enough to readily allow

a serial interface, which helps limit the package size of the ADC.

MAX1281"

Maxim's 10

was chosen because it meets all of the requirements in a small, TSSOP

package.

Bluetooth Wireless Communication Module

We determined early in the project that a commercial module using the new

Bluetooth protocol12 would be the most straightforward way of achieving the highbandwidth wireless connection we required. Bluetooth was designed for short-distance

wireless connectivity between small, low-power devices, and its spread-spectrum,

frequency hopping protocol was made to limit interference from ambient electromagnetic

noise. The data rate of 725 kbits per second (kbps) was acceptable but not outstanding,

especially compared to the 11 Mbps rates of wireless Ethernet cards. However, size and

power consumption were very high priorities; wireless Ethernet adapters are larger than

the entire space allotted to TEAS, and modules in packages other than those for plugging

into laptop PC card slots were not available.

The available Bluetooth modules were

effectively single components approximately the size of our other large components such

20

as the FPGA, and the Bluetooth module thus fit the TEAS approach of using commercial,

of-the-shelf parts.

The availability of Bluetooth modules in PC card format only

improved the attractiveness of Bluetooth as the wireless communication module because

less work would be necessary on the external interface: the Bluetooth card would

effectively be all the hardware required for the entire external interface, and all that we

would need to implement on the PC side would be software.

The prototype Bluetooth module is Cambridge Silicon Radio unit13 that is truly a

self-contained radio, unlike some alternatives that required external amplifiers or filters.

The 23 mm x 15 mm module has a standard asynchronous serial interface that provides

access to several layers of the protocol stack. One interface, HCI, allows the unit to be

controlled with relatively simple commands without detailed understanding of the

frequency-hopping algorithm. Most of the complexity is in setting up a connection; once

it is established, sending data is relatively straightforward. The only real problem is in

achieving the advertised bandwidth of 725 kbps: the highest data rate we have achieved is

approximately 500 kbps.

The TEAS analog electronics and wireless connection are

detailed by Johann Burgert.

Digital Electronics

The digital electronics system must read the analog-to-digital converters, process

the incoming data, and send the processed data to the Bluetooth module. The digital

section also contains the microcontroller, which governs the entire implant by controlling

the power supplies for the rest of the electronics. The front end of the digital electronics,

which must interface to eight serial ADCs simultaneously, is implemented on a field

programmable gate array (FPGA). The FPGA includes the circuitry for interfacing to a

small external SRAM that is used for peak detection. The FPGA also controls a large

SRAM to buffer data that the microcontroller will read and transmit to the Bluetooth

module. A block diagram of the digital electronics is shown in Figure 11. The digital

section is the focus of this document, and its design will be discussed thoroughly in

Chapter 3 of this thesis.

21

ADDR<11:0>

DATA<13:0>

EIGHT

8-CHANNEL

ADCs

---

SCLK

*

uCOD

uCADDR<7:0> 4

uCDATA<11:0>

BUFSIZE<2:0>

LOADBUFSIZE 4

SOUT<7:0>

SIN<7:0>

C

16-BIT

MICROCONTROLLER

*C

FPGA

OI

At

A

(P A

00

NEWDATA

OVERFLOW

RESULT< 7:0>

ACK

BLUETOOTH

_

LU

RESET

--

(9

16 MHz

CLOCK

4k x 16 SRAM

64 RING BUFFERS

CLK

<0

t

4*

2M x 8 SRAM

TRANSMIT FIFO

BUFFER

Figure 11: Digital electronics block diagram.

Power System

The power system consists of a rechargeable battery, the necessary accessories for

wirelessly charging that battery, and several voltage regulators that provide the correct

voltages to different parts of the electronics system. Most of the volume of the power

system, the battery and recharging circuit, can be implanted in the abdomen of a test

monkey, and the size of the system is therefore not a primary concern. The battery will

be a lithium-ion or lithium-polymer battery that has a nominal voltage of 3.6 volts. The

battery must have a capacity of approximately 13 kJ (1 amp-hour at 3.6 V), which will

allow for three hours of operation with the estimated 1 W power consumption of the

electronics.

To recharge the battery in a reasonable amount of time (overnight), the

charging circuit must deliver 100 mA. Work on this portion of TEAS has been very

limited, but preliminary designs have been able to charge the battery at 50 mA through a

22

10-mm separation.

Power management is critical to the design, and every component was chosen

with power consumption in mind. Table 1 gives a breakdown of the estimated power

consumption of the electronics, assuming 3.0 V operation. A lithium-ion or lithiumpolymer battery can readily provide the necessary current of 330 mA. There are four

separate voltage regulators on TEAS: one for the microcontroller, one for the rest of the

digital electronics, a third for the analog electronics, and a fourth for the Bluetooth

module. The microcontroller coordinates the functions of the electronics system, so it

must always be powered. The microcontroller can independently shut down the power to

the analog front end, the FPGA and SRAMs, and the wireless communication system.

The microcontroller can internally switch to an extremely low power mode that allows

the minimum average current consumption of the entire electronics system to be below 1

mA, which is necessary during charging and periods when the device is not in use. In

this low-power mode, the microcontroller can monitor charging status and occasionally

power up the communications system to check for any incoming commands.

Table 1: Power budget for TEAS electronics, assuming a 3.0 V power supply.

Analog Electronics

Amplifiers

ADCs

Total

Bluetooth Module

Digital Electronics

FPGA

2 MB SRAM

64 KB SRAM

Microcontroller

Clock

Total

Total for All Electronics

23

360 mW

60 mW

420 mW

180 mW

225

75

45

15

30

mW

mW

mW

mW

mW

390 mW

990 mW

3. Digital Electronics Design

The interface to the digital electronics section of TEAS was determined very early

in the project. The primary input to the system would be the data from eight 8-channel,

12-bit analog-to-digital converters (ADCs), and the system would process that data and

send any detected neural spikes to the Bluetooth module over an approximately 1 Mbps

serial link. The system would also have a secondary input in the form of a serial input

from the wireless link, over which any TEAS system commands would be received. As

with the rest of the project, the most important design constraints were size, power

consumption, and ready availability of components.

High-Level Design Choices

Given the requirements, there were two general design approaches that could have

been pursued. The system must read a very wide parallel input from eight ADCs, and it

must generate a completely serial output; the two main alternatives to dealing with the

parallel input were:

" using a high-speed microprocessor or digital signal processor and tackling the

problem in software;

" implementing custom parallel hardware.

The two options, and why we ultimately chose the parallel hardware approach, are

described next.

The High-Speed Processor Alternative

Using a high-speed processor was appealing since a single programmable device,

and thus a single development environment, would be necessary for the design. Also,

having greater available processing power in the implant might allow for more complex

triggering or better compression algorithms that would make better use of the limited

wireless transfer rate.

The main problem with the approach was that it was not

necessarily feasible, and even if it were, there might not be any time left after reading the

ADCs for the extra processing that made the approach attractive in the first place. The

24

requirement of sampling 64 channels at a minimum of 30 kHz makes the minimum

aggregate sampling rate 1.92 MHz.

Even with a processor such as a 200 MHz

StrongARM, a processor typical in high-end handheld computers, only 100 cycles per

sample would be available. A hundred cycles may initially seem more than adequate, but

the main problem is that, since the 64 channels are processed sequentially, the samples

from the individual channels are interlaced: after reading a sample, 63 other samples must

be processed before reaching the next sample for the first channel. A substantial portion

of the available processing time would thus be spent context switching. Even without the

context switching, a hundred cycles is not much time for analyzing a sequence of

samples, which would be necessary for advanced triggering or compression. To make

matters worse, the processor must also deal with the asynchronous communication with

the wireless module, whose small buffer must remain full to ensure optimal transfer rates,

and which may at arbitrary times receive new commands from the external user interface.

In addition to not having clear performance benefits, the single-processor option

wasn't clearly smaller or less power hungry than the parallel hardware approach. Highperformance processors typically do not have the level of system and peripheral

integration seen on smaller 8-and16-bit processors, which often have program memory,

data memory (SRAM), and hardware serial ports in one package. The high-performance

processor would thus not present a one-component solution to the digital system and

would instead require space comparable to that for the parallel-hardware approach chosen

for TEAS. The high processor speed and the need for additional components would also

make the power requirements similar to that of the alternative approach.

Besides the

consumption of the digital hardware alone, the high-speed system would also require

ADCs that are faster and therefore more power hungry.

A final disadvantage to the high-speed approach is that it would significantly

complicate the PCB layouts for prototypes and the final implant. Creating layouts for

high-speed digital electronics is not trivial even without consideration of how it might

interfere with the analog electronics or the wireless communication module. Because of

the lack of clear advantages to the high-speed approach and because of the added

complexity, we chose the parallel hardware alternative.

25

The Parallel Hardware Alternative

The parallel hardware approach, however, is not without its own issues. One of

the problems is that the required output of the digital system was ultimately not parallel,

and the data from the 64 channels need to be organized into a single serial stream

somewhere in the system.

Furthermore, interfacing to the Bluetooth module requires

complex protocols that are very difficult to implement as a straight hardware solution.

Therefore, a combination of programmable logic and a microcontroller is used for the

TEAS digital section. The downside to this design choice is that it required finding two

major components: the microcontroller and the programmable logic device (PLD).

It is worth noting that the conceptually different components of microcontroller

and PLD need not be physically distinct or in different packages. Many PLDs are large

enough to contain several large microprocessors, and pre-designed code for emulating a

processor in a PLD is readily available. More recently, devices that explicitly combine a

microcontroller with a PLD in one package have become available.

For example,

Atmel's15 Field Programmable System-Level Integrated Circuit (FPSLIC) 16 contains, in

one package, a 30,000-gate field programmable gate array (FPGA), an 8-bit Atmel AVR

microcontroller, and an SRAM bank accessible from both the FPGA and the

microcontroller. Unfortunately for TEAS, these single-chip solutions were more capable

than necessary for TEAS, and, as a result, they were too large and power hungry. The

multi-component approach has the advantage of allowing selection of components with

the minimal capabilities necessary to achieving the task at hand; different components

can also be completely powered down to minimize power consumption during idle or

recharging periods.

An important aspect to the microcontroller and PLD design was to break up the

tasks efficiently and to develop an interface between the two components.

This early

design decision was especially important since component selection is critical to the

success of the project, and large-scale changes might not be possible to implement once

components were chosen. Thus, the parallel-hardware approach, given that it could not

be implemented using just one component, was in some ways less flexible than the high26

speed controller approach. On the other hand, the parallel approach allows for more

independent implementation of subsections of the design, and thus allows a more

structured design approach that uses hierarchy and abstraction. For example, changing

the ADC interface protocol with the high-speed approach might cause timing changes

that would require significant rewriting of the processor code; with the parallel-hardware

approach, the change would be contained within a programmable logic unit that

interfaces to the ADC, and the microcontroller code wouldn't have to change at all.

The tradeoffs between the two approaches are dependent on the number of

channels that TEAS must record. Beyond 100 channels, the high-speed approach would

almost certainly have been impossible, but even a mid-range microprocessor could

readily have handled ten channels. With the 64 required channels, either approach could

probably have been implemented.

Ultimately, the parallel-hardware approach was

chosen for TEAS because it was more likely to result in a smaller, less power-hungry

design in a shorter amount of time.

Compression Considerations

The Bluetooth wireless connection is a huge bottleneck. Even with the theoretical

maximum bandwidth of 725 kbps, less than one thirtieth of the 2 million 12-bit samples

collected every second can be transmitted. By itself, buffering the data does not help

much because it piles up at the huge rate of almost 24 Mb per second. With the lack of

abundant memory in the implant and with a very slow connection to the outside world,

some form of compression prior to transmission is clearly necessary.

An important

design requirement from the Brown neuroscientists was that, should there be any

compression, it would have to be lossless, with the exception that they were only

interested in the neural spikes and their timing.

Indeed, triggering on neural spikes and sending only the spike information

provides a huge reduction in required bandwidth. Unfortunately, the compression factor

varies with the neural spiking rate, which can vary from 10 to 300 Hz. With individual

spikes lasting approximately 1.5 ms, the interesting data comprise 1.5% to 45% of all

collected data. If the average spiking rate were below 20 Hz, spike detection alone would

27

provide the thirty-fold compression necessary to compensate for the discrepancy between

the acquisition and transmission rates. Additional compression, however, would still be

desirable since only four channels spiking at a high rate would overwhelm the

electronics.

Given that the general shape of neural signals is known, it seems likely that that

knowledge could be used to effectively compress the spikes themselves. However, the

lossless compression requirement eliminated many substantial compression options.

Algorithms used for compressing electrocardiograph (EKG) readings, which have shapes

similar to neural signals, typically achieve 90% compression, but that compression comes

mostly from eliminating the uninteresting data between heartbeats, much like the spike

detection discussed above. Another major impediment to using knowledge about the

spikes' expected shape is the interlaced sampling of individual channels, which results in

samples for individual channels being scattered through memory.

It is not clear that any general-purpose compression approach would yield

appreciable benefits when applied to the interlaced signals. Even test runs of LempelZiv"

compression on non-interlaced spike samples (obtained from existing neural

recording systems) were unsuccessful. Given that the individual channel samples are

independent, interlaced samples of detected peaks are effectively random, making

lossless compression without first recovering the data structure almost impossible.

Achieving practical compression in real time would thus be challenging on a highperformance desktop computer, let alone on the limited microcontroller used in the TEAS

implant.

One last explored approach was delta-compression right in the front-end, parallel

hardware of the digital electronics.

This approach would require, for each channel,

additional storage for one sample that would always hold the previous sample value.

Then, instead of wirelessly sending the sample values, the differences would be sent-the

hope being that the range of changes would be much smaller than the range of values.

Unfortunately, some parts of the spikes have very steep slopes, and with the added

necessity of a sign bit to indicate the direction of the change, this simple scheme saved

only one or two bits per sample: in our tests, delta-compression required approximately

28

10 bits per sample. While the 17% compression would be nice to have, units of 10 bits

are difficult to work with because 10 is not a power of two. Since the digital electronics

components are all organized with 8- or 16-bit busses, taking advantage of the two saved

bits would require much more manipulation of the samples to pack them into 8- or 16-bit

chunks. Combined with the added hardware requirements to do the subtraction on-thefly, the added complexity was not worth the potential payoff.

Thus, it was determined that the nature of our data did not allow for simple

compression and there was insufficient processing power on the implant to do more

complicated compression in real time. Thus, TEAS relies on a relatively low average

spiking rate on the sampled electrodes to keep the transmit buffer from overflowing. To

lower the negative impact of the low-spiking-rate requirement, the user interface will

allow the researcher to turn off any channels that correspond to inactive electrodes or that

are otherwise uninteresting. The number of samples per spike can also be varied, up to

the extreme where only the time for each spike is sent; in that mode, the available

bandwidth can support all 64 channels spiking at 300 Hz.

Breaking Up the Digital Section

Given the design decisions to implement a parallel-hardware approach and to

limit compression to straight neural spike detection, the next task was to determine how

the digital section should be broken up between the programmable logic device and the

microcontroller.

Provided that a good division into separate sections could be

determined, those sections could then be implemented almost independently. Component

selection would be closely tied to this choice because of the general TEAS design

approach of rapid development using readily available components. Once components

were selected, it would be costly and time consuming to change the section divisions in a

way that exceeded what was achievable within the flexibility of the chosen components.

The programmable logic section clearly had to take care of the ADC interface.

Spike detection and pre-trigger buffering was also appropriate for the high-speed logic

since a lot of data had to be pushed around quickly. The microcontroller, on the other

hand, was selected primarily for dealing with the Bluetooth module and higher-level

29

control of the entire implant.

It became clear from these task assignments that the

following section separation was appropriate: the programmable logic would do all

incoming data processing and asynchronously present the microcontroller only with data

to be transmitted over the wireless link; and the microcontroller would, at its own

discretion, arbitrarily read data from the programmable logic section and write to the

High-level communication protocol

implemented in microcontroller to

send data to external system

Microcontroller

Asynchronously accessible

digital representation of

neural spikes in original input

Programmable

Digital Logic

Performs peak detection

to pick out relevant data

Clean, digital representation

of original input

Analog Electronics

Weak signals are amplified

and digitized

Analog

Input

Electrodes are like antennas

that pick up very weak signals

Electrode Array

Figure 12: Abstraction and hierarchy in the TEAS electronics design.

Bluetooth module. Except for some initial setting up of thresholds and other parameters,

this arrangement allows the microcontroller to be oblivious to the details of the data being

collected: to the microcontroller, the programmable logic section is just a black box from

which data can be read at any time, indistinguishable from any other parallel data source

such as FIFO. The microcontroller must then implement a high-level protocol to get the

data to the external logging system without any errors. The hierarchy and abstraction for

30

the entire TEAS electronics design is shown in Figure 12.

Information (neglecting

handshaking signals) flows in only one direction, and each level insulates the next level

from many of the details of the signals the brain implant is recording.

31

The Programmable Logic System

The general breakdown described above makes the programmable logic system

the heart of the data acquisition system within the implant. As its input, the system has

eight analog-to-digital converters that it must also control. The output is a FIFO buffer

that can be read at any time by the microcontroller, which is generally oblivious to the

contents of the data and just deals with getting them, uncorrupted, to the external system;

the format of the data can therefore be determined by the programmable logic system.

The output buffer of the programmable logic section also serves as a secondary transmit

buffer since the microcontroller and Bluetooth module have very limited buffers. Since

the microcontroller reads data from the programmable logic unit only when the Bluetooth

module can take more, this output buffer must be as large as possible to prevent bursts of

neural activity from overwhelming the system. Of course, the programmable logic must

also perform its central role of carrying out peak detection and time-stamping on the

incoming data. There are thus four main sections to the programmable logic system: the

ADC interface, the triggering or spike detection system, the transmit buffer controller,

and global counter. These sections are examined in detail after a description of the

components used to implement the design.

Choosing Components, Part 1: Programmable Logic Device Selection

Choosing the programmable logic device for TEAS was something of a chickenand-egg problem: it was difficult to select a device without first knowing more about

what would be put on it, but those very details of the design were not necessarily

independent of the device that was chosen. Many devices had special features that might

have been useful, but the potential usefulness could not really be evaluated without

designing a substantial portion of the system around those features.

One feature that

would have been especially useful was integrated SRAM, which could have been used

for individual channel buffers used for recording peaks; however, the smaller devices that

were candidates for TEAS did not have sufficient memory.

Special features were

ultimately ignored because they were difficult to evaluate, and because using them would

require specialized development environments.

32

Even comparing general sizes or

densities was difficult because each manufacturer, and even different product lines from

the same manufacturer, had different measures of features and performance. Complex

programmable logic devices (CPLDs) are typically measured in terms of number of

macrocells, whereas the main parameter with field-programmable gate arrays (FPGAs) is

usually the number of programmable gates.

To make a better-informed decision, a general design was made in VHDL

(VHSIC (Very High Speed Integrated Circuit) Hardware Description Language); the

design itself is described below. The preliminary design effectively eliminated CPLDs

because of their limited size.

The CoolRunner series of CPLDs from Xilinx18 had

seemed particularly attractive, and a version with 512 macrocells might have been large

enough for the design; unfortunately, that version was not expected to be available for

many months. The Delta39K series from Cypress" promised CPLDs at FPGA densities,

but they were also just in development. Other CPLD lines typically do not have more

than 256 macrocells.

The lack of sufficiently large CPLDs was unfortunate because

SRAM-based FPGAs need to be configured every time they are turned on, requiring an

additional component that stores the configuration file in a non-volatile format.

With FPGA densities being much higher than those of CPLDs, the primary

parameters to look for became small physical size and low power consumption. Given

that the device would require over 100 1/0 lines, the some form of BGA (ball grid array)

packaging was essential. Power consumption was very difficult to judge because it is

very dependent on the particular configuration of the device. Ultimately, the Flex 1 0k30A

device from Altera2 0 was chosen for TEAS. The FlexlOk3OA 2 was available in a 1-mmpitch BGA package that was just 17 mm on a side (see Figure 13), had 30,000 usable

gates, had the lowest claimed power consumption, and, perhaps most importantly, was

immediately available. Once the FlexlOk3OA was chosen, the design was refined around

that part. The device is available in several different speed grades, but speed wasn't too

much of an issue because the design requires clock speeds under 20 MHz, which is

extremely slow for FPGAs.

33

Figure 13: The FPGA is one of the largest components in the design.

Choosing Components, Part 2: Transmit Buffer SRAM and Ring Buffer SRAM

Due to the huge difference between the possible data acquisition rate and the

maximum wireless transfer rate, obtaining a very large memory component for the

transmit buffer was crucial to achieving high performance in TEAS. Unfortunately for

the small development team with a very low expected production volume of TEAS units,

competing with large cell phone and handheld computer manufacturers, who also wanted

small, high-density memories, was very difficult. Many manufacturers would not speak

to a potential customer unless he was interested in at least thousands of units, and the

newest, smallest, highest-density devices were not available through distributors that

2

were willing to deal with small quantities, such as Digi-Key1 . Also, single-chip SRAMs

typically go up to about 8 Mbits in size, which is only enough for approximately 150

spikes per channel. While this number of spikes is acceptable, the buffer could

potentially fill up in a matter of seconds. A larger SRAM would hold more spikes, which

would make the buffer more effective because fluctuations in neural firing rates occur at

time scales close to those during which a smaller buffer could overflow. Fortunately,

24

Toshiba" provided sample units of a new 16-Mbit SRAM, the TC55W1600FT , which

has very low power consumption and comes in a TSOP48 package that measures 20 mm

x 12 mm. The SRAM is one of the largest components on TEAS, but it is crucial to

34

smooth operation during periods of higher neural spiking, which is usually especially

interesting. The TC55W1600FT was also particularly appealing because the memory can

be accessed as IM x 16 or 2M x 8, which allowed commitments to bus widths to be

made later.

Besides the large buffer SRAM, a smaller SRAM would be necessary to

temporarily hold data samples prior to triggering. The SRAM needed to have a bus width

of at least 12-bits to allow rapid sample transfer without shuffling around individual bits

separately from each other; since 12-bit bus widths aren't typical, a 16-bit device was

necessary. Such devices are abundant, so availability, power consumption, and package

size were used to choose the Cypress CY62126BV2 5 , which comes in a 48-ball BGA that

measures just 7 mm x 7 mm. Since it is very difficult to work with BGA packages,

another SRAM with the same interface but in a TSOP32 package was used for

prototyping. Ultimately, however, finding and using the smallest available packages is

crucial to achieving the required TEAS size.

ADC Interface

The analog section uses eight Maxim MAX1281 single-supply, low-power, 8channel, 12-bit, serial ADCs. The serial interface is used both for reading samples and

for setting ADC parameters such as channel selection and power mode. The MAX1281

uses Serial Peripheral Interface (SPI), a synchronous serial protocol supported by many

8-bit microcontrollers. The digital section front end must serve as the SPI "master" for

all eight ADCs by generating the serial clocks and initiating conversions.

The main points of the MAX1281 interface are shown in Figure 14, which shows

how the ADC would be used with a microcontroller that has SPI support. First, the

controller must send an 8-bit control word, which specifies parameters such as the

channel to be sampled. The first bit of the control byte must always be set, and it initiates

a conversion. After the control byte is sent, two bytes are read back. The two bytes

contain the 12-bit result, padded with one leading zero and three trailing zeros. A single

conversion therefore takes 24 serial clock cycles. The data for both input and output lines

are always valid on the rising edge of the serial clock.

35

12

8

14

16

24

20

SCLK

DOUT

DIN

A2 AlIA0 u

PD1 PDOI

MSB

D D101 D91 D8 D7 D6 D5 D4 D31 D21 D

START

S

Control Byte

LSB

DOI

o

ADC Result

A2:AO - channel selection

UNI/BIP - 1 = unipolar, 0 = bipolar

SGL/DIF - 1 = single ended, 0 = differential

PD1,PDO - power mode select

Figure 14: ADC interface timing diagram for reading one sample.

The interface can be run more quickly when the input and output transactions are

not constrained to 8-bit units, as shown in Figure 15. A control byte can be sent every 16

clock cycles, provided that the conversion result can be picked out at the correct time,

which is very simple with the programmable logic used in TEAS. The overlap of input

and output operations allows a much faster sampling rate, and the overlap is necessary to

achieve the 30 kHz minimum sampling rate required of the TEAS system.

1

24

16

8

32

SCLK

DOUT

DIN

S CONTROL BYTE 1

S CONTROL BYTE 0

I

CONVERSION RESULT 0

CONVERSION RESULT 1

*

Figure 15: ADC interface timing for reading a sample every 16 clock cycles.

Since there are no constraints on the timing of parallel conversions among the

eight ADCs, the control byte and serial clock can be the same for all eight 8 ADCs.

Therefore, the initial ADC interface design, shown in Figure 16, had a single output shift

register, the output of which would connect to all eight ADCs. All eight results would

therefore also appear simultaneously on eight separate result lines. Each ADC control

channel on the FPGA had a corresponding input unit consisting of a receive shift register

36

and a receive buffer. A properly timed "load" signal would transfer the contents of the

shift registers to the buffers, providing the next stage of the digital system with eight

buffers that always contained the most recent samples from the eight ADCs.

To

SCLK

JI

-

--

sclk

4

ADCOAD7channel

-

-

---

- -

I1

Se

power

power:,

down

3

To DIN

on

ADCOADC7

channel

.3

SEL2:0 0111

init

init

8

Transmit Shift Register

shift

shift

-- -.-..............

ADCO DOUT

P,

:Serial I

In

LSB

Receive Shift Register

shift

i i i

MSB

12

load:

Receive Buffer

2

AD]O

A DC I

ADC2

ADC3

ADC4

ADC5

ADC6

D OU T

DOUT-Al

O

DOUT

DOUT

DOUT DOUT-

ADC7 DOUT

- -... -........

-................

ADC result ,

AORESULT

lR S L

RESULT

-........ ......

A2

A3

A4

A5

9

........................

A 6...R

E...U LT.

A6

RESULT

Receive Shift Register

Serial

In

-

.......... ...

.....

...........

LSB

12

Receive Buffer

12

RESULT

RESULT

RESULT

RESULT

12

shift:

MSB

load

ADC resultA7

..

..

..

..

..

...

....

..

..

..

...

..

...

..

..

..

..

...

..

.....

....

..

..---1

iP

U

2

A7 RESULT

Figure 16: Initial, highly parallel ADC interface block diagram.

The original design described above adheres strictly to the parallel-hardware

approach of the digital section: the hardware for all eight ADCs is a set of exact replicas

that take eight parallel inputs and provides eight parallel outputs that can be used

37

downstream by additional parallel hardware. However, later refinements to the next

stage of the digital system, the triggering system, made simultaneous availability of all

eight ADC results unnecessary. As described in the overview of the digital system, the

output of the digital section must be sequential, so the change from parallel to serial must

happen somewhere within the digital section. Implementing parallel versions of small

digital modules such as the input shift registers is simple, but achieving parallel memory

access is much more difficult. Given that the triggering system (described in the next

section) uses an external SRAM to store ADC results, implementing truly parallel

memory access would require multiple external SRAM components along with many

parallel address and data busses. The size and power restrictions on TEAS make multiple

SRAMs unattractive, if not unfeasible, so some form of multiplexing of a single SRAM is

required. Given that ADC samples are stored in a single SRAM sequentially, it becomes

unnecessary for all eight ADC samples to be available simultaneously and at all times.

The above conclusion was used to make the current ADC interface a more

efficient, more tightly integrated part of the digital system. Instead of sending the control

byte simultaneously to all eight ADCs, the output section sends eight different versions of

the control byte, each staggered by two clock cycles; the starting times of the ADCs are

thus evenly distributed throughout the 16-cycle sample period.

The results are then

received every two cycles, and instead of using a receive buffer on every input channel, a

multiplexer selects the shift register that currently holds a valid result. The multiplexed

result can then be buffered if it is needed for both cycles or used directly if the triggering

system only needs the result at the beginning of the time it has allotted to each channel.

Some attention must be paid to the details of the interface to synchronize the current

multiplexer result with the rest of the system. The lower bits of a global counter are used

to indicate the current channel being processed, and the ADC interface must make the

correct result available at the correct time. Because of the delay between starting a

conversion and getting the result, the serial output section must add one to the channel

number requested for the result to match the global counter. (This addition of one is not

strictly necessary since the electrode numbers could just be relabeled; however, a 3-bit

increment is very minimal, and it reduces the possibility of confusion in the electrode-to38

channel-number mapping, which is already complicated by PCB layout issues.)

GLOBALCOUNTER8:1

CHANNEL

1

3

1

SEL2:0 1 1 1 1

I

I

I

I

I

I

I. .

I

I

I I

I

load

8

23-bit Transmit Shift Register

I

sh ift

I I I I

I I I I

DOUT7

DOUT6

DOUT5

DOUT4I

DOUT3

DOUT2

DOUTO

DOUTO

SCLK 4

-

1

Receive Shift Register

1

11

Ishift

0

SEL

/

12

ADC2 DOUT

12

ADC3 DOUT

12

ADC4 DOUT

I

/

12

ADC5 DOUT

ADC6 DOUT

3

MSB

0

LSB

ADCI DOUT

/

41

. ..

..

12

'

'12

ADC7 DOUT

12

ADC8 DOUT

S12

Figure 17: Final ADC interface block diagram.

39

parallel

result for

current

12 12channel

The final version of the ADC interface is shown in Figure 17. The elimination of

the input buffers in the original, more parallel version is significant because the eight

buffers required 108 flip-flops. The new version does require more transmit hardware,

but the size of the ADC interface as a whole is almost halved. A reduction in size is

almost always useful since it reduces constraints when fitting the design onto the FPGA.

Although the ADC results are presented sequentially, the interface to the rest of the

digital system is very clean: the ADC module reads the global counter, and always

outputs the ADC result for the channel specified by the counter. The ADC interface thus

puts some additional constraints on the rest of the system by eliminating the possibility of

any additional parallel hardware, but a sequential approach to the rest of the system is

both required by the external SRAM and likely to lead to a more compact overall design.

The interface assumes a serial clock speed of 4 MHz, which results in an aggregate

sampling rate of 2 MHz and an individual channel sampling rate of 31.25 kHz. The serial

clock can potentially be increased up to 4.8 MHz (37.5 kHz per channel), which is the

upper limit for the MAX1281. The VHDL source code for the ADC interface is listed in

Appendix A3 and Appendix A4.

Spike Detection System

The output of the ADC interface is read by the spike detection unit, which is the

central component of the TEAS data acquisition system since it determines which data

are saved and transmitted outside of the implant. Because data samples are stored in a

single external SRAM, the triggering system processes each channel sequentially,

requiring this processing to execute very quickly. Fortunately, the triggering mechanism

can be as simple as a comparator that checks to see if the incoming data values exceed a

predetermined threshold. However, the spike detection system is more complicated than

the trigger mechanism alone because it must keep track of additional state. A spike is

detected only after the spike is well under way, so all samples must temporarily be saved

even without a channel having triggered. After triggering, the relevant saved samples

must be sent to the large transmit buffer, but this relatively simple-sounding task is

complicated once again by the lack of processing time, which requires most tasks to be

40

broken up.

The spike detection system is thus perpetually switching contexts, and

designing an effective method of quickly saving and retrieving the state of individual

channels was critical.

Depicted in figure 18 is the expected data waveform of a neural spike, along with

some of the terms that are used in the description of the spike detection system. A spike

is detected, and a channel triggers, when a sample exceeds the channel's threshold value.

A certain number of samples are pre-storedbefore triggering, and additional samples are