LHO 07 - Lab 5 and The Linear Feedback Shift

advertisement

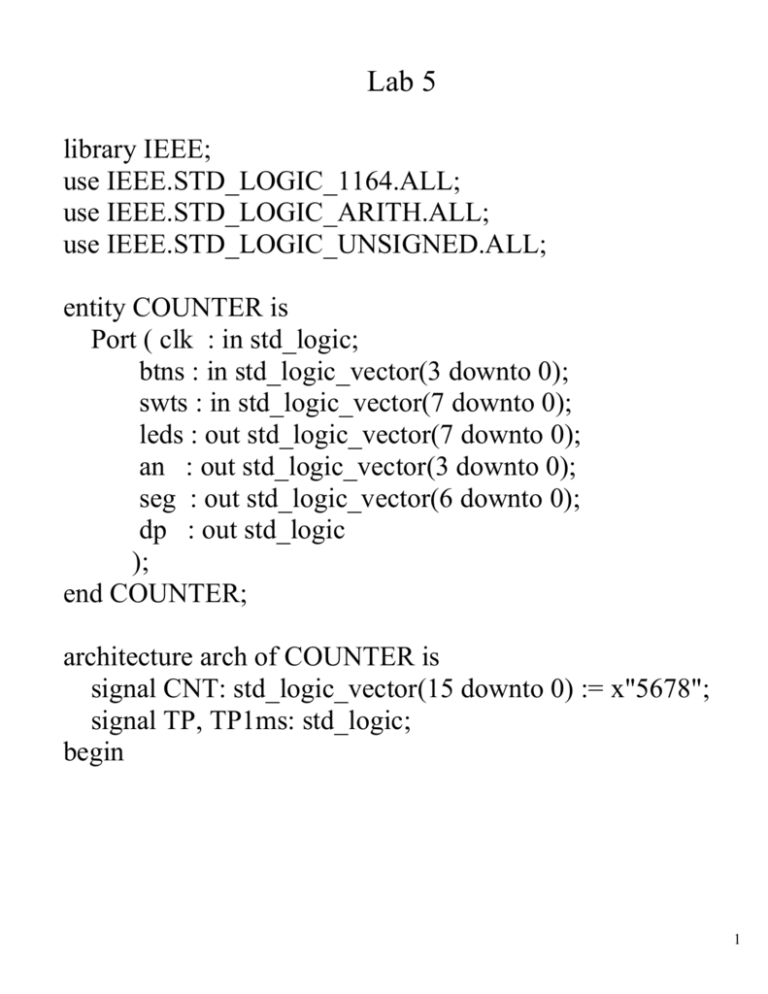

Lab 5 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity COUNTER is Port ( clk : in std_logic; btns : in std_logic_vector(3 downto 0); swts : in std_logic_vector(7 downto 0); leds : out std_logic_vector(7 downto 0); an : out std_logic_vector(3 downto 0); seg : out std_logic_vector(6 downto 0); dp : out std_logic ); end COUNTER; architecture arch of COUNTER is signal CNT: std_logic_vector(15 downto 0) := x"5678"; signal TP, TP1ms: std_logic; begin 1 -- Generate tick for counter. U1MS: entity work.NCNT(arch) generic map(50000) port map (CLK, TP1ms); UTP: entity work.ENCNT(arch) generic map(100) port map (CLK, TP1ms, TP); -- Use seven segment display to show elapsed time. U_SSD: entity work.NSSD(arch) port map (CLK => CLK, hex => CNT, DP => "0001", DISP_SEG(7) => dp, DISP_SEG(6 downto 0) => seg , Disp_AN => an, EN => '1'); -- Connect swts to LED's leds <= swts; -- Generate count process(clk) begin if clk'event and clk = '0' then if TP = '1' then if btns /= 0 then CNT <= (others => '0'); elsif swts /= 0 then if CNT < 9999 then CNT <= CNT + 1; end if; end if; end if; end if; end process; end arch; 2 3 4 5 6 The Linear Feedback Shift Register tap table. Constant taps : tap_table := ( 7 8 9 Example consider n = 3 (3 flip-flops). From the table for n = 3 we look up (1,0,-1,1); thus if we label the flip-flops as: Q2, Q1, Q0, the D0 = Q1, D1 = Q2 and D2 = Q1 Q0. The counting sequence is Q2 Q1 Q0 1 1 1 0 1 1 0 0 1 1 0 0 0 1 0 1 0 1 1 1 0 1 1 1 ... Ex 3 bit LSR D2 <= Q1 Q0, D1 <= Q2, D0 <= Q1 Ex 16: bi <= (bi(5) xor bi(3) xor bi(2) xor bi(0)) &bi(15 downto 1) after 5 ns; 10 Example: Consider a LFSR when n = 8. From the table we look up (6, 5, 1, 0); thus, D7 = Q6 Q5 Q1 Q0. Implementing this on the DE2 and outputting to the leds of the DE2 can be done as follows: library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; use IEEE.numeric_std.all; entity DE2_lfsr is Port ( clk : in std_logic; LEDs : out unsigned(7 downto 0)); end DE2_lfsr; architecture Behavioral of DE2_lfsr is signal TP1us, TP1ms, Tslow : std_logic; begin U1: entity ECNT generic map(50) port map (CLK, '1', TP1us); U2: entity ECNT generic map(1000) port map (CLK,TP1us,TP1ms); U3: entity ECNT generic map(200) port map (CLK, TP1ms, Tslow); process (CLK) variable Led_out: unsigned(7 downto 0); begin if clk'event and clk = '0' and Tslow = '1' then if Led_out = 0 then -- Make machine self correcting from all 0 state. Led_out := (others => '1'); Else -- Generate LFSR Led_out := (Led_out(6) xor Led_out(5) xor Led_out(1) xor Led_out(0)) & Led_out(7 downto 1); end if; -- Output to LED’s Leds <= Led_out; end if; end process; end Behavioral; 11