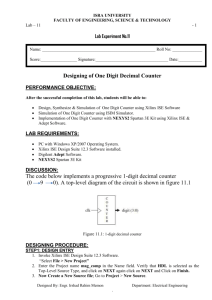

how to create file in xilinx

advertisement

Founded in Silicon Valley in 1984 Xilinx ISE Software Xilinx® Integrated Software Environment (ISE) software. COE758 - Xilinx ISE 9.2 Creating Simple Project Start Xilinx ISE software, and press OK on “Tip of the Day” to get to a screen as shown above Create new project by selecting File->New Project New window will open. Project location – select the directory for the projects Project Name – select project name. Notice how directory with same project name is added in the Project Location text field. Press Next> In the Device Properties selection of the device and package is done. Family: Spartan3E Device: XC3S500E Package: FG320 Speed: -5 Preferred Language: VHDL Keep the rest of the settings and press Next> In this window you can either add new source , or leave it for later as it is done in this tutorial. Press Next> several times until finish and press Finish on the last window. When new project is created source files can be added. Right click on the device and select New Source. New Wizard window is opened Select VHDL Module and enter the name of the vhdl source file. Press Next> In this window input and output signals are specified. Notice that for led and switch signals Bus checkbox is selected and size of the bus is specified. Press Next> Last window in the wizard shows summary of the source including inputs and outputs for that module. Press Finish to add source file to project. When source file is added ISE tool window should look as above Next step is to add actual processing source code. Sample VHDL program library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; Library definitions entity tutorial is Port ( clk : in STD_LOGIC; led : out STD_LOGIC_VECTOR (7 downto 0); switch : in STD_LOGIC_VECTOR (3 downto 0)); end tutorial; Input/Output definitions architecture Behavioral of tutorial is signal counter: std_logic_vector(29 downto 0); counter definition begin process(clk) begin if(clk'Event and clk='1') then if(switch(0)='1') then counter<=counter+'1'; else counter<=counter-'1'; end if; end if; end process; led(7 downto 0)<=counter(29 downto 22); end Behavioral; Counter counting up if switch is on, and counting down if switch is off. Every addition occurs on every positive clock edge. Output of the top bits of counter on LEDs When program is written its syntax can be checked by expanding Synthesize and double clicking on Check Syntax. If errors are found, double click on error and correct the mistake. When all of the errors were corrected and Synthesis has been completed successfully an assignment of inputs and outputs has to be done. Since FPGA is already mounted on the development platform inputs and outputs are restricted and have to be specified. Only ones that are used have to be specified in the constraint file. Add new source same way as before, but this time select Implementation Constraint File, and specify name for the constraint file. Press Next> UCF constraint file is added to the VHDL file. Select constraint file and double click on Edit Constraints (Text) Enter constraints for the LEDs and Switches that are located in the lower right corner. Clock signal for all of the designs is connected to pin “C9” on FPGA When code is debugged and constraint file is correctly entered we can generate a configuration file. Right click on Generate Programming File and select Run. Similarly as before, if errors occur, double click on the error and correct it. If configuration file is generated successfully we can load it on to the platform. Expand Generate Programming File, right click on Configure Device (iMPACT) and select Run. iMPACT wizard window will open. Select top option of configuring using JTAG and press FINISH. On the initial iMPACT load wizard will prompt to select configuration files for all of the devices present on the JTAG chain. Press Esc key for all of the windows. Right click on the left device which represents Spartan 3E FPGA and select Assign New Configuration File To load program on the FPGA device, right click on the FPGA icon and select Program. Programming properties window will be shown. On the Programming Properties make sure verify is UNCHECKED. Press OK at which point configuration file will be uploaded to FPGA.