Sector Processor Main FPGA Choice

advertisement

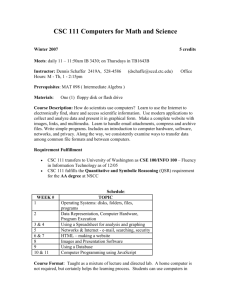

March 15, 2002 Lev Uvarov Sector Processor Main FPGA Choice Petersburg Nuclear Physics Institute / University of Florida Rev 1.0 March 14, 2002 Summary Main FPGA choice is discussed in detail. Table 1 summarizes the chip I/O usage. It also counts the required number of signal pins for mezzanine card connectors. The appropriate candidates appear to be Virtex II XC2V3000 or bigger devices into FF1152 packages. The total number of mezzanine card connector pins exceeds the current mezzanine card design by almost 150 and reaches almost 730. It is very unlikely that ALCT and SP could share the same mezzanine card. Main FPGA Functionality Main FPGA of the SP2002 prototype performs reconstruction of complete tracks from individual track segments delivered to it from both Endcup Muon (EMU) CSC chambers over front panel optical links and Front FPGAs and Barrel Drift Tubes (DT) over Transition board, see Figure 1. Whereas EMU track segments are already aligned in time into the Front FPGAs, DT track segments still need to be aligned into the Main FPGA. The CCB and VME interface provides VME access to the Main FPGA chip, as well as delivers timing control signals from the CCB. The DDU interface ensures collecting of DT track segments and reconstructed tracks into the event frame on the L1A request. The Main FPGA drives address and control lines of PT LUTs. It also allows loading PT LUTs with data using an additional buffer, which provides a data path to the LUT I/Os. PT LUT is a 4Mx8 Static RAM (SRAM) implemented either as two Toshiba 4Mx4 TC55V4400FT devices, or as two Toshiba 2Mx8 TC55V8200FT devices with access time of 10-15 ns. Each bunch crossing the SP2002 sends to the Muon Sorter (MS) 64 bits of data at a double rate of 80 MHz, organized in two 32-bit frames, Figure 2. LVTTL/GTLP translators are Fairchild GTLP16617 devices and feature synchronous output enable, allowing clean wired multiplexing on their outputs. Other features include: • Medium drive GTLP capability of 50 mA; • Flow-through pinout; • 6.7/8.7ns CLKAB to B-out maximum delay. In each GTLP16617 transceiver internal triggers sample A-inputs at 80MHz, but only every other sample reaches the transceiver output. Which one succeeds is determined by the CLK40-90 and CLK40-270 signals applied to the /OEAB transceiver enable inputs. LU-SP_Main_FPGA_Choice_1d0.doc Page 1 of 5 March 15, 2002 Lev Uvarov 9xD24 ME2/ ME4 STUBS Main FPGA C3 3xD12 + 4xD1 9xD5 3xD1 MUX 3xA22 6xD24 ME1 STUBS PT LUT 3xC4 6xD9 3xD8 2xD1 D8 3xC1 DT STUBS 3xD8 2xD25 BUF 3xD8 C1 C2 DDU INT C8 D16 C3 CFG ROM C2 CCB & VME INT C10 A8 D16 Legend: G – Number of Signal Groups GxAn – G Groups of n Address Lines GxCn – G Groups of n Control Lines GxDn– G Groups of n Data Lines CCB & VME INT – Combined CCB and VME Interface BUF – Buffer PT LUT – PT Assignment Look Up Table CFG ROM – Configuration EEPROM DDU INT – Readout Interface ME1 STUBS – ME1 CSC Track Segments ME2/ME4 STUBS – ME2, ME3, and ME4 CSC Track Segments DT STUBS – Drift Tube Track Segments MUX - Multiplexer Figure 1 Sector Processor Main FPGA Dataflow Main D32 FPGA D8 LVTTL /GTLP FRAME2 D32 Back Plane A22 Legend: Ax – x Address Lines Dx – x Data Lines Cx – x Control Lines C4 PT LUT D8 A22 C4 PT LUT D8 PT LUT D8 D32 LVTTL /GTLP FRAME1 D32 A22 C4 WIRED MUX /OEAB=CLK40-90 /OEAB=CLK40-270 CLKAB=CLK80 Figure 2 PT LUT and Multiplexer Details LU-SP_Main_FPGA_Choice_1d0.doc Page 2 of 6 March 15, 2002 Lev Uvarov Table 1 Main FPGA I/O Count Virtex-II I/O Pin Count Signal Name Dir 3.3V VME Interface VM_D I/O VM_A I /VM_WR I /VM_CE I Subtotal ME2-ME4 Muons CSC_VP CSC_Q CSC_PHI CSC_PHIB CSC_ETA CSC _BC1 Sum Comment 16 12 1 1 30 1 1 1 1 16 12 1 1 30 16 12 1 1 30 VME Data VME Subaddress Space [A8:A1] Write Enable (AL-Active Low) Chip Select (AL) 1 4 12 5 7 1 9 9 9 9 9 3 9 36 108 45 63 3 9 36 108 45 63 3 Valid Pattern Quality Phi Azimuthal Angle Phi Bend Angle Eta Global Angle Bunch Crossing One, once per orbit 264 264 6 24 72 30 42 24 2 6 24 72 30 42 24 2 200 200 3.3V or 2.5V I I I I I I Subtotal 30 3.3V or 2.5V ME1 Muons CSC_VP CSC_Q CSC_PHI CSC_PHIB CSC_ETA CSC_ID CSC _BC1 I I I I I I I Subtotal 1 4 12 5 7 4 1 6 6 6 6 6 6 2 34 3.3V I I I I I I I DT Muons DT_Q DT_PHI DT_PHIB DT_BXN DT_Flag DT_Synch DT_CLK40 Subtotal MS Mux SP_PHI SP_ETA SP_HALO Bits Groups Connectors Pin Count 3.3V O O O Valid Pattern Quality Phi Azimuthal Angle Phi Bend Angle Eta Global Angle CSC ID Bunch Crossing One, once per orbit 3 12 5 2 1 1 1 25 2 2 2 2 2 2 2 6 24 10 4 2 2 2 50 6 24 10 4 2 2 2 50 Quality Phi Azimuthal Angle Phi Bend Angle Bunch Crossing Second Muon Flag Synchronization / Calibration Clock40 5 5 1 3 3 3 15 15 3 15 15 3 Phi Azimuthal Angle Eta Angle Halo Muon Trigger LU-SP_Main_FPGA_Choice_1d0.doc Page 3 of 6 March 15, 2002 Lev Uvarov Virtex-II I/O Pin Count Signal Name SP_CHARGE SP_BXN SP_ERROR SP_SPARE MX_CLK Subtotal SP to PT LUT 4M x 8 TC55V4400FT x 2 PT_DPHI PT_SIGN PT_ETA PT_MODE /PT_CE /PT_WE /PT_OE Subtotal Buffer (for PT LUT loading) BUF_D /BUF_OE /BUF_DIR Subtotal DDU Readout DDU_D DDU_VP DDU_RR DDU_RA DDU_ST DDU_RSVD Subtotal Fast Control CCB_CLK40 CCB_CLKEN CCB_BC0 CCB_BCR CCB_TEST CCB_L1A CCB_SPARE Subtotal Fast Monitoring FM_OSY FM_SPARE Subtotal Configuration Dir O O O O O 3.3V O O O O O O O 3.3V O O O 3.3V O O I O I I/O 3.3V I I I I I I I 3.3V O O Bits Groups 1 3 2 1 1 1 1 1 3 1 19 Connectors Pin Count Sum 3 2 1 1 3 43 3 2 1 1 3 43 Comment Muon Sign 2 LSB of BXN Error Spare Mux Clocks 13 1 4 4 1 1 2 26 3 3 3 3 3 3 3 39 3 12 12 3 3 6 78 39 3 12 12 3 3 6 78 Delta Phi Azimuthal Angle Sign Eta Angle Mode Chip Enable (AL) Write Enable (AL) Output Enable (AL) 8 1 1 1 3 1 8 3 1 12 8 3 1 12 Data Chip Enable (AL) Output Enable (AL) 16 1 1 1 1 3 23 1 4 1 1 1 1 16 4 1 1 1 3 26 16 4 1 1 1 3 26 Readout Data Valid Pattern Readout Request Request Acknowledge Readout Start Readout Reserved 1 1 1 1 1 1 2 8 1 1 1 1 1 1 1 1 1 1 1 1 1 2 8 1 1 1 1 1 1 2 8 Main Clock Clock Enable Bunch Counter Zero Bunch Counter Reset Test Request L1 Accept Reserved 1 1 2 1 1 1 1 2 1 1 2 Out of Synch Reserved 3.3V LU-SP_Main_FPGA_Choice_1d0.doc Page 4 of 6 March 15, 2002 Lev Uvarov Virtex-II I/O Pin Count Signal Name Dir CFG_M I CFG_DIN I CFG_DOUT O CFG_INIT I/O CFG_CCLK I CFG_PROG_B I CFG_DONE I/O Subtotal 3.3V JTAG Modes CFG_TMS I CFG_TDO O CFG_TDI I CFG_TCK I Subtotal Bits Groups 3 1 1 1 1 1 1 1 1 1 1 1 1 1 9 1 1 1 1 Connectors Pin Count Sum 3 0 1 1 1 1 4 716 726 1 1 1 1 1 1 1 TOTAL Comment Configuration Mode Bits Serial Input Serial Output Delay Configuration Configuration Clock Hard Reset from CCB Completion of Configuration 3 1 1 1 1 1 1 9 Test Mode Select Test Data Out Test Data In Test Clock XC2V3000-5FF1152C or bigger The total number of required I/Os for Main SP2002 FPGA reaches 716. Error! Not a valid bookmark self-reference. gives us available number of user I/Os for each device/package combination of the Virtex-II FPGA series. The applicable candidates are devices in FF1152 package (highlighted in light green). Table 2 Virtex-II Device/Package Combinations and Maximum Number of Available I/Os Package Virtex-II Available I/Os XC2V 40 XC2V 80 XC2V 250 XC2V 500 XC2V 1000 CS144 88 92 92 FG256 88 120 172 172 172 200 264 324 FG456 FG676 FF896 432 XC2V 1500 XC2V 2000 XC2V 3000 392 456 484 528 624 FF1152 720 FF1517 BG575 328 392 XC2V 4000 XC2V 6000 XC2V 8000 824 824 824 912 1104 1108 684 684 684 408 BG728 456 516 BF957 624 684 The smallest XC2V3000 device provides as many as 720 user I/Os, whereas XC2V4000 and bigger devices – 824 I/Os. The preliminary number of required user I/Os is very close to 720, and using the smallest device may become an obstacle for development as design progresses and request for more I/Os emerges. LU-SP_Main_FPGA_Choice_1d0.doc Page 5 of 6 March 15, 2002 Lev Uvarov Mezzanine Card Considerations It is assumed that the Main FPGA chip is located on the mezzanine card, square in shape, which is stacked to the main board using 4 Samtec FOLC/MOLC connectors. The FOLC/MOLC interconnect system features 4-row of 2 mm pitch contacts, and up to 50 contacts per row. 200 contacts per connector, or 800 contacts in total give enough flexibility for SP2002 board routing. Table 3 Revision Histories Date February 26, 2002 March 14, 2002 Revision # Initial Proposal Rev 1.0 What’s new Figure 1 completely updated. EMU Muon box has been split into two boxes for ME2/ME4 and ME1 track segments respectively. LU-SP_Main_FPGA_Choice_1d0.doc Page 6 of 7