Review

advertisement

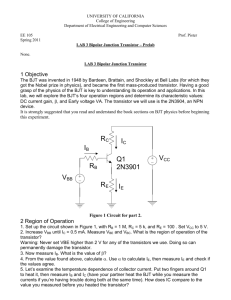

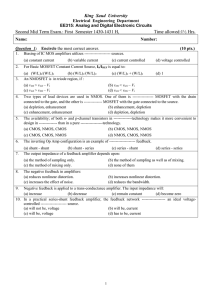

Diodes Transistor Types? MOSFET Circuit Symbols • (g) and (i) are the most commonly used symbols in VLSI logic design. • MOS devices are symmetric. • In NMOS, n+ region at higher voltage is the drain. • In PMOS p+ region at lower voltage is the drain. NMOS Transistor iD Kn' W vDS v V GS vDS TN 2 L ' K W 2 iD n vGS VTN 2 L for vDS vGS VTN ' K n W 2 v V 1 v iD GS TN DS 2 L MOSFET Bias Analysis Example VGS2 0.05VGS 7.21 0 VGS 2.71V,2.66V Problem: Find Q-pt (ID, VDS) Approach: Assume operating region, find Q-point, check to see if result is consistent with operation region Since VGS < VTN for VGS = -2.71 V and MOSFET will be cut-off, VGS 2.66 V and ID 34.4 A Also, VDD ID(RD RS )VDS and VDS 6.08 V VDS > VGS -VTN . Hence saturation region assumption is correct. Q-pt: (34.4 A, 6.08 V) with VGS = 2.66 V Bias Analysis Example 2 (Two-Resistor biasing for PMOS Transistor) Also 15V (220k)ID VDS 0 2 15V (220k) 50 A2 VGS 2 VGS 0 2 V VGS 0.369V, 3.45V Assumption: IG = IB = 0, transistor is saturated (since VDS = VGS) Analysis: VGS (470k)IG VDS 0 Since VGS = -0.369 V is less than VTP = -2V, VGS = -3.45 V ID = 52.5 A and VGS = -3.45 V VDS VGS VTP Hence saturation assumption is correct. Q-pt: (52.5 A, -3.45 V) MOSFET as a Current Source • Ideal current source gives fixed output current regardless of voltage across it. • MOSFET behaves as as an ideal current source if biased in the pinch-off region (output current depends on gate-source terminal voltage). NMOS Current Mirror I REF K W n V V GS1 TN 1 V 2 DS1 2 L K W 2 IO n VGS2 VTN 1 V DS2 2 L But VGS2 VGS1 and Assumption: M1 and M2 have identical VTN, Kn’, and W/L and are in saturation. 1 VDS2 IO IREF IREF 1 VDS1 Thus, the output current precisely mirrors the reference current if VDS1 = VDS2. MOS Current Mirror Ratio 1 V W /L 1 VDS2 DS2 2 IO IREF 5IREF W /L1 1 V 1 V DS1 Kn1 Kn' W 2Kn' L 1 W ' Kn2 Kn 10Kn' L 2 DS1 IO 5IREF Thus, the ratio between IO and IREF be modified by changing the can W/L ratios of the current mirror transistors (ignoring differences due to VDS mismatch) N-Channel JFET i-v Characteristics iD I for Transfer Characteristics DSS 1 2 GS P v 1 vDS V vDS vGS VP 0 Output Characteristics npn Bipolar Transistor: Forward Characteristics Base current is given by iB iF F IS BE T v exp V F 1 20 F 500 is forward common-emitter current gain Emitter current is given by iE iC iB Forward transport current is S BE T iC iF I exp v V 1 IS is saturation current 10 18 IS F BE T v exp V 1 F 0.95 F 1.0 is forward common F 1 base current gain In this forward active operation region, iC A IS 10 A 9 iB VT = kT/q =0.025 V at room temperature F iC iE F i-v Characteristics of Bipolar Transistor: Common-Emitter Output Characteristics For iB = 0, transistor is cutoff. If iB > 0, iC also increases. For vCE > vBE, npn transistor is in forward-active region, iC = F iB is independent of vCE. For vCE < vBE, transistor is in saturation. For vCE < 0, roles of collector and emitter reverse. Chap 5 - 12 Operation Regions of Bipolar Transistors Base-Emitter Junction Base-Collector Junction Reverse Bias Forward Bias Forward Bias Forward-Active Region (Good Amplifier) Saturation Region (Closed Switch) Reverse Bias Cutoff Region (Open Switch) Reverse-Active Region (Poor Amplifier) Binary Logic States Chap 5 - 13 i-v Characteristics of Bipolar Transistor: Common-Emitter Transfer Characteristic Defines relation between collector current and base-emitter voltage of transistor. Almost identical to transfer characteristic of pn junction diode Setting vBC = 0 in the collector-current expression yields S BE T v iC I exp V 1 Collector current expression has the same form as that of the diode equation Chap 5 - 14 pnp Transistor: Forward Characteristics Base current is given by iB Forward transport current is S EB T iC iF I exp v V F IS F v exp V iE iC iB I 1 1 EB T 1 Emitter current is given by S iF F 1 EB T v exp V 1 Four-Resistor Bias Network for BJT V EQ VCC R1 REQ R1 R2 R1 R2 R1 R2 R1 R2 V EQ REQIB VBE RE I E 4 12,000IB 0.716,000(F 1)IB V EQ VBE 4V- 0.7V IB 2.68 A 6 R ( 1)R 1.2310 EQ F IC F IB 201 A F 75 E IE (F 1)IB 204 A VCE VCC RC IC RE I E C RF VCE VCC R IC 4.32 V F Forward active region assumption is correct – Q-point is (201 A, 4.32 V) BJT Current Mirror S VCE1 VBE IS exp 1 2 I REF V V A FO T VCE 2 1 VBE VCE 2 VA 1 I IC 2 I S exp REF VBE V V T A 1 2 VA FO VCE2 1 I VA MR O I REF 1 VBE 2 VA FO VBE I exp V T With infinite FO and VA, mirrorratio MR is unity. Finite current gain and Early voltage introduce mismatch between output and reference current of mirror BJT Current Mirror: Output Resistance • Output current from BJT current mirror depends on voltage across it, due to finite Early voltage. 1 io iC2 IREF 1 VCE2 VBE VA 1 VA IREF 2 FO 1 VBE VA vo VA 2 FO • Ro is the small-signal output resistance of the current mirror. 1 Ro o o Q pt i v O A I 1 O V V VA IO Linear Amplification A complex periodic signal can be represented as the sum of many individual sine waves. Consider only one component with amplitude Vs and frequency ws : vs Vs sinwst Amplifier output is sinusoidal with same frequency but different amplitude VO andphase : vo Vo(sinwst ) BJT Amplifier BJT is biased in active region by dc voltage source VBE. Q-point is set at (IC, VCE) = (1.5 mA, 5 V) with IB = 15 A. Total base-emitter voltage is: vBE VBE vbe Collector-emitter voltage is: vCE 10iCRC This is the load line equation. BJT Amplifier (cont.) If changes in operating currents and voltages are small enough, then iC and vCE waveforms are undistorted replicas of input signal. Small voltage change at base causes large voltage change at collector. Voltage gain is given by: Vce 1.65180 Av 206180 206 V 0.0080 8 mV peak change in vBE gives 5 A be change in iB and 0.5 mA change in iC. Minus sign indicates 1800 phase shift V 0.5 mA change in iC produces a 1.65 between input and output signals. change in vCE . Coupling and Bypass Capacitors C1 and C3 are large-valued coupling capacitors or dc blocking capacitors whose reactance at the signal frequency is designed to be negligible. • AC coupling through capacitors is used to inject ac input signal and extract output signal without disturbing Q-point • Capacitors provide negligible impedance at frequencies of interest and provide open circuits at dc. C2 is a bypass capacitor that provides a low impedance path for ac current from emitter to ground, thereby removing RE (required for good Q-point stability) from the circuit when ac signals are considered. dc Equivalent for BJT Amplifier • All capacitors in original amplifier circuits are replaced by open circuits, disconnecting vI , RI , and R3 from circuit. ac Equivalent for BJT Amplifier RB R1 R2 10k 30k R RC R3 4.3k100k Hybrid-Pi Model of BJT Transconductance: IC gm y21 40IC VT Input resistance: • The hybrid-pi small-signal model is the intrinsic representation of the BJT. • Small-signal parameters are controlled by the Q-point and are independent of geometry of the BJT r 1 oVT o y21 IC gm Output resistance: 1 VA VCE VA ro y22 IC IC Small-Signal Parameters of MOSFET Transconductance: gm y21 • Since gate is insulated from channel by gate-oxide input resistance of transistor is infinite. • Small-signal parameters are controlled by the Q-point. • For same operating point, MOSFET has higher transconductance and lower output resistance that BJT. 2I D VGS VTN 2K n I D Output resistance: ro 1 1 VDS 1 y22 I D I D Amplification factor for VDS<<1: f gmro 1 VDS I D 2K n ID 1 Small-Signal Model of JFET For small-signal operation, the input signal limit is: vgs 0.2VGS VP Since JFET is normally operated with gate junction reversebiased, The amplification factor is given by: 1 f gmro 2 VDS 2 VGS VP VP I ISG rg G IDSS ID Amplifier Power Dissipation • Static power dissipation in amplifiers is determined from their dc equivalent circuits. Total power dissipated in C-B and E-B junctions is: Total power dissipated in transistor is: PD VDS ID VGSIG VDS ID PD VCE IC VBE IB where VCE VCB VBE Total power supplied is: PS VCCIC VEE IE Total power supplied is: PS VDDID Two-port Model for 3-stage Cascade Amplifier • Each amplifier in the 3-stage cascaded amplifier is replaced by its 2-port model. RinB RinC A A vo AvAvs vB vC R R R R outA outB inB inC Av If Rout = 0 vo vs AvAAvBAvC Rin= RinA and Rout= RoutC = 0 Source and Load Resistances: Voltage Amplifier With Thévenin equivalent of input source: If Rin >> Rs and Rout<< RL, Av A In an ideal voltage amplifier, Rin and Rout = 0 Vo vo Av1 v1 vs RL Rout RL Rin Ai RS Rin Vo Rin RL Av A Vs RS Rin Rout RL Io I1 RS Rin Ai Av RL Vs RS Rin RL Vo RS Rin Vs RL Inverting Amplifiers: Common-Emitter and Common-Source Circuits ac equivalent circuit for C-E Amplifier ac equivalent for C-S Amplifier Follower Circuits: Common-Collector and Common-Drain Amplifiers ac equivalent for C-C Amplifier ac equivalent for C-D Amplifier Noninverting Amplifiers: Common-Base and Common-Gate Circuits ac equivalent for C-E Amplifier ac equivalent for C-S Amplifier NMOS Transistor Capacitances: Saturation Region CGS 2 CGC CGSOW 3 CGD CGDOW Cox” = Gate-channel capacitance per unit area(F/m2). CGC = Total gate channel capacitance. CGS = Gate-source capacitance. CGD = Gate-drain capacitance. CGSO and CGDO = overlap capacitances (F/m). SPICE Model for NMOS Transistor Typical default values used by SPICE: Kn or Kp: KP = 20 A/V2 g: GAMMA= 0 : LAMBDA = 0 VTO = 1 V or VTO = -1 V n or p UO = 600 cm2/V-s 2 FF: PHI = 0.6 V CGDO = CGSO = CGBO = CJSW = 0 Tox: TOX = 100 nm BJT SPICE Model • Besides capacitances associated with the physical structure, additional components are: diode current iS and substrate capacitance CJS related to the large area pn junction that isolates the collector from the substrate and one transistor from the next. • RB is resistance between external base contact and intrinsic base region. • Collector current must pass through RC on its way to active region of collectorbase junction. • RE models any extrinsic emitter resistance in device.