Transistor Characterization Lab Report

advertisement

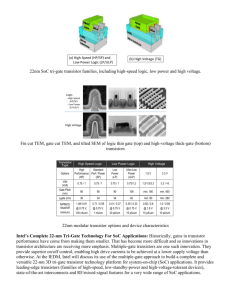

Report # 1: Due Week of 1/24/05. READ THIS BEFORE THE LAB AS WELL AS BEFORE LEAVING THE LAB TO ENSURE THAT YOU HAVE ALL DATA NEEDED TO COMPLETE THE REPORT The lab report consist of a brief summary, describing the experiment, its goal and purpose and the key results and conclusions. In addition answer the following questions in sequence. Place graphs, pictures and other material gathered during the lab period in the report with a caption. Do not attach it as an appendix. Report questions: a) List the color of all three oxides. Provide the top and cross-sectional view of the transistor you observed in the lab. Add a picture of the layout to your report. Draw a stick diagram as well as a circuit diagram. Identify the input(s), output(s), power supply and ground. Is it an analog or digital circuit? Can you identify the function of this circuit? b) What is the output conductance (gd = dID/dVDS) of the transistor you measured? Indicate the gate voltage at which you measured the output conductance. Include the I-V curve plot in your report. Add a figure caption. c) What is the threshold voltage of that same transistor as obtained from the versus VGS curve? Attach the plot to your report. Fit the measured curve to the following expression: |ID| |ID| = /2 |VGS - VT| and extract the parameter p Cox W/L. From the parameter (= K) find the hole mobility p in the channel and compare it to the bulk hole mobility in the substrate. Assume the substrate is a 2 cm phosphorous-doped wafer and an oxide thickness tox = 80 nm. d) Obtain an expression for the transconductance when the transistor is in saturation. Use the data from part c) to find a numeric value for the transconductance at the same gate voltage you obtained the output conductance (part b). Calculate the ratio of the transconductance to the output conductance. This ratio equals the maximum voltage gain one can obtain with this transistor. e) Construct a PSPICE model for the transistor you measured. Use the model to plot the square root of ID versus VGS in saturation. Use LEVEL 1 and LEVEL 2 for the pMOS model and compare the curves by overlaying them on the same graph. Which LEVEL reproduces most closely the experimental curves? Which LEVEL provides the most accurate model? Explain the difference between the two. Additional experiment(s) f) Plot the threshold voltage as a function of the bulk-source voltage and compare it to the expected value from equation (7.4.9) (webbook 7.4.2) by plotting both on a single graph. What is the substrate doping density which provides the best fit. Is this value consistent with the resistivity of the wafer ( = 2 cm) ? g) Plot the measured slope as a function of the bulk-source voltage. Is the quadratic model (webbook 7.3.2) adequate to describe the observed variation?