303hF09HW4_sol

advertisement

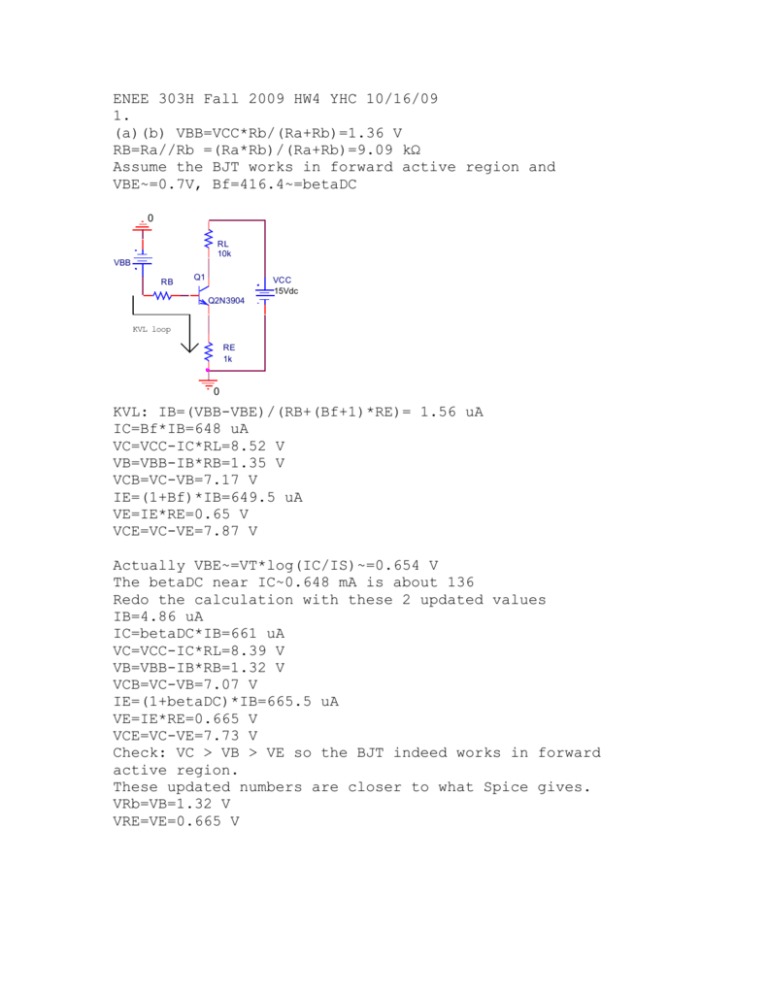

ENEE 303H Fall 2009 HW4 YHC 10/16/09

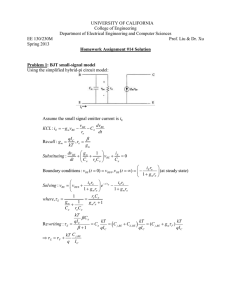

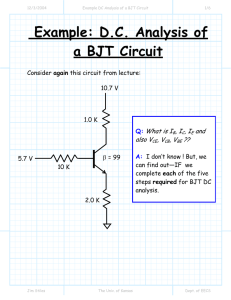

1.

(a)(b) VBB=VCC*Rb/(Ra+Rb)=1.36 V

RB=Ra//Rb =(Ra*Rb)/(Ra+Rb)=9.09 kΩ

Assume the BJT works in forward active region and

VBE~=0.7V, Bf=416.4~=betaDC

0

RL

10k

VBB

RB

Q1

VCC

15Vdc

Q2N3904

KVL loop

RE

1k

0

KVL: IB=(VBB-VBE)/(RB+(Bf+1)*RE)= 1.56 uA

IC=Bf*IB=648 uA

VC=VCC-IC*RL=8.52 V

VB=VBB-IB*RB=1.35 V

VCB=VC-VB=7.17 V

IE=(1+Bf)*IB=649.5 uA

VE=IE*RE=0.65 V

VCE=VC-VE=7.87 V

Actually VBE~=VT*log(IC/IS)~=0.654 V

The betaDC near IC~0.648 mA is about 136

Redo the calculation with these 2 updated values

IB=4.86 uA

IC=betaDC*IB=661 uA

VC=VCC-IC*RL=8.39 V

VB=VBB-IB*RB=1.32 V

VCB=VC-VB=7.07 V

IE=(1+betaDC)*IB=665.5 uA

VE=IE*RE=0.665 V

VCE=VC-VE=7.73 V

Check: VC > VB > VE so the BJT indeed works in forward

active region.

These updated numbers are closer to what Spice gives.

VRb=VB=1.32 V

VRE=VE=0.665 V

Spice:

NAME

MODEL

IB

IC

VBE

VBC

VCE

BETADC

Q_Q1

Q2N3904

4.86E-06

6.62E-04

6.53E-01

-7.06E+00

7.71E+00

1.36E+02

RE=500 Ω,

IB

IC

VBE

VBC

VCE

BETADC

8.79E-06

1.22E-03

6.70E-01

-1.54E+00

2.21E+00

1.39E+02

RE=2k Ω,

IB

IC

VBE

VBC

VCE

BETADC

2.72E-06

3.49E-04

6.35E-01

-1.02E+01

1.08E+01

1.28E+02

(c)

Ra

100k

RL

10k

PARAMETERS:

Q1

Rpar

VCC

15Vdc

Q2N3904

Rb

10k

RE

{Rpar}

0

1.4mA

1.2mA

1.0mA

0.8mA

0.6mA

0.4mA

0.2mA

0.4K

IC(Q1)

0.6K

0.8K

1.0K

1.2K

Rpar

1.4K

1.6K

1.8K

2.0K

12V

10V

8V

6V

4V

2V

0V

0.4K

VE(Q1)

0.6K

0.8K

VC(Q1)

VC(Q1) - VE(Q1)

1.0K

1.2K

1.4K

1.6K

1.8K

2.0K

Rpar

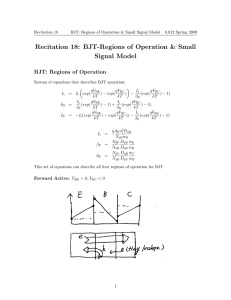

As RE increases,

1. IC decreases (so does IB, IE, VBE) because the effective

resistance from collector to ground increases.

2. VCE increases (so does VCB). Higher VCE can provide

larger signal swing (before BJT saturates).

3. The voltage drop on RL decreases.

4. IE becomes less sensitive to beta variation

(RE >> RB/(1+beta)).

2.

KP W

(a) I D

2 L

VSG p Vt 0 p

p

=

2

2mA, solve VSGp=4.575 V

This is an approximation value since we have to

take channel length modulation

(the term 1+lambda*VSD) into account.

See the implementation of the current sources in the

following circuit. We can perform a VSGp DC sweep to make

Iin and Iin1 get even closer to 2mA.

VSGP8

4.45Vdc

M4007P

M8

PARAMETERS:

VSGP7

4.36Vdc

Vpar

M5

VDD

15Vdc

M6

V6

{Vpar}

M4007P

M7

M4007N M4007N

{Vpar}

VDS2

M1

M2

M3

M4007N M4007N

M4

M4007N M4007N

0

(b) Saturation condition: VDS VGS Vt

In class it has been shown that VG(M2) is fixed at 4.49

V, so VD(M2)>=4.49-1.3=3.19 V. Similarly, VG(M4)=4.49 V,

VG(M6)= 2*VG(M4)= 8.98 V, so VD(M6)>=8.98-1.3=7.68 V

We improve the output resistance of current mirror at

the expense of using higher VD.

(c)

2.4mA

2.0mA

1.6mA

1.2mA

0.8mA

0.4mA

0A

0V

2V

ID(M2)

ID(M6)

4V

ID(M2) - ID(M6)

IS(M7)

6V

IS(M8)

8V

10V

12V

14V

16V

Vpar

It’s found that for the cascode current mirror the curve is

much flatter (that is, the Early effect is reduced a lot).

The output resistance is amplified by a factor about

gm6*ro6 (p.649 of Sedra/Smith).

With VG(M6) being and VS(M6) not fixed, this allows the

ID(M6) increase caused by VDS increase can be reduced by

VGS decrease.

Because in saturation region ID is more sensitive to VGS,

it has been shown in class that for VD6 = 10 and 12 V, a

small VGS drop (0.04 V) is able to compensate the much

bigger VDS increase (2.04 V).