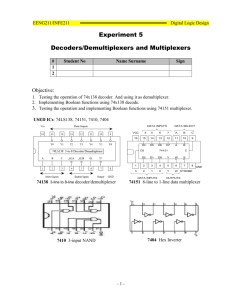

CECS470

advertisement

Combinational Logic Building Blocks • Decoders: – Binary n-to-2n decoders. – Implementing functions using decoders. • Encoders: – 2n -to-n binary decoders. • Three-State Buffers. • Multiplexers. • Demultiplexers EECC341 - Shaaban #1 Lec # 9 Winter 2001 1-10-2002 Decoders • A decoder is a multiple-input, multiple-output logic circuit that converts coded inputs into coded outputs, where the input and output codes are different. e.g. n-to-2n, BCD decoders. • Enable inputs must be on for the decoder to function, otherwise its outputs assume a single “disabled” output code word. Input Code word Decoder Map Output code word Enable inputs EECC341 - Shaaban #2 Lec # 9 Winter 2001 1-10-2002 Decoder Example: Seven-Segment Decoders /Bl 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 -- don’t care inputs -- • A seven segment decoder has 4-bit BCD input and the seven segment display code as its output: • In minimizing the circuits for the segment outputs all non-decimal input combinations (1010, 1011, 1100,1101, 1110, 1111) are taken as don’t-cares DC x x 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 1 1 0 1 0 1 0 1 0 1 1 1 1 1 1 1 1 B x 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 A x 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 a 0 1 0 1 1 0 1 0 1 1 1 0 0 0 1 0 0 b 0 1 1 1 1 1 0 0 1 1 1 0 0 1 0 0 0 c 0 1 1 0 1 1 1 1 1 1 1 0 1 0 0 0 0 d e 0 0 1 1 0 0 1 1 1 0 0 0 1 0 1 1 0 0 1 1 0 0 1 1 1 0 0 0 1 0 1 1 0 0 f 0 1 0 0 0 1 1 1 0 1 1 0 0 1 1 1 0 g 0 0 0 1 1 1 1 1 0 1 1 1 1 1 1 1 0 EECC341 - Shaaban #3 Lec # 9 Winter 2001 1-10-2002 Binary n-to-2n Decoders • A binary decoder has n inputs and 2n outputs. • Only the output corresponding to the input value is equal to 1. n inputs : n to 2n decoder : 2n outputs EECC341 - Shaaban #4 Lec # 9 Winter 2001 1-10-2002 2-to-4 Binary Decoder Truth Table: X 0 0 1 1 • • Y F0 0 1 1 0 0 0 1 0 F1 F2 F3 0 0 0 1 0 0 0 1 0 0 0 1 F0 = X'Y' F1 = X'Y From truth table, circuit for 2x4 decoder is: F2 = XY' Note: Each output is a 2variable minterm (X'Y', X'Y, XY' or XY) F3 = XY F0 X Y 2-to-4 Decoder X Y F1 F2 F3 EECC341 - Shaaban #5 Lec # 9 Winter 2001 1-10-2002 3-to-8 Binary Decoder Truth Table: F0 = x'y'z' x 0 0 0 0 1 1 1 1 y 0 0 1 1 0 0 1 1 z F0 0 1 1 0 0 0 1 0 0 0 1 0 0 0 1 0 F1 0 1 0 0 0 0 0 0 F2 0 0 1 0 0 0 0 0 F3 0 0 0 1 0 0 0 0 F4 0 0 0 0 1 0 0 0 F5 0 0 0 0 0 1 0 0 F6 0 0 0 0 0 0 1 0 F7 0 0 0 0 0 0 0 1 F1 = x'y'z F2 = x'yz' F3 = x'yz F4 = xy'z' F5 = xy'z F6 = xyz' F0 Y Z F7 = xyz F1 X 3-to-8 Decoder F2 F3 F4 F5 F6 x y z F7 EECC341 - Shaaban #6 Lec # 9 Winter 2001 1-10-2002 Implementing Functions Using Decoders • Any n-variable logic function, in canonical sum-of-minterms form can be implemented using a single n-to-2n decoder to generate the minterms, and an OR gate to form the sum. – The output lines of the decoder corresponding to the minterms of the function are used as inputs to the or gate. • Any combinational circuit with n inputs and m outputs can be implemented with an n-to-2n decoder with m OR gates. • Suitable when a circuit has many outputs, and each output function is expressed with few minterms. EECC341 - Shaaban #7 Lec # 9 Winter 2001 1-10-2002 Implementing Functions Using Decoders • Example: Full adder S(x, y, z) = S (1,2,4,7) C(x, y, z) = S (3,5,6,7) 3-to-8 0 Decoder 1 x S2 y S1 z S0 2 3 4 5 6 7 x 0 0 0 0 1 1 1 1 y 0 0 1 1 0 0 1 1 z 0 1 0 1 0 1 0 1 C S 0 0 0 1 0 1 1 0 0 1 1 0 1 0 1 1 S C EECC341 - Shaaban #8 Lec # 9 Winter 2001 1-10-2002 Standard MSI Binary Decoders Example 74138 (3-to-8 decoder) (a) Logic circuit. (b) Package pin configuration. (c) Function table. EECC341 - Shaaban #9 Lec # 9 Winter 2001 1-10-2002 Encoders • If the a decoder's output code has fewer bits than the input code, the device is usually called an encoder. e.g. 2n-to-n, priority encoders. • The simplest encoder is a 2n-to-n binary encoder, where it has only one of 2n inputs = 1 and the output is the n-bit binary number corresponding to the active input. • For an 8-to-3 binay encoder with inputs I0-I7 the logic expressions of the outputs Y0-Y2 are: Y0 = I1 + I3 + I5 + I7 Y1= I2 + I3 + I6 + I7 Y2 = I4 + I5 + I6 +I7 2n inputs . . . Binary encoder . . . n outputs EECC341 - Shaaban #10 Lec # 9 Winter 2001 1-10-2002 8-to-3 Binary Encoder At any one time, only one input line has a value of 1. I0 I1 Inputs I0 1 0 0 0 0 0 0 0 I1 0 1 0 0 0 0 0 0 I2 0 0 1 0 0 0 0 0 I3 0 0 0 1 0 0 0 0 I4 0 0 0 0 1 0 0 0 Outputs I5 0 0 0 0 0 1 0 0 I6 0 0 0 0 0 0 1 0 I7 0 0 0 0 0 0 0 1 y2 0 0 0 0 1 1 1 1 y1 0 0 1 1 0 0 1 1 y2 0 1 0 1 0 1 0 1 Y2 = I4 + I5 + I6 + I7 I2 I3 y 1 = I2 + I 3 + I6 + I7 I4 I5 I6 I7 Y0 = I1 + I3 + I5 + I7 EECC341 - Shaaban #11 Lec # 9 Winter 2001 1-10-2002 Three State (Tri-State) Buffers • Three state buffers are CMOS and TTL devices whose outputs may be in one of three states: 0, 1 or Hi-Z (high impedance, or floating state. • Have an extra input called “output enable” or “output disable”. • When enables the device transmits the input value or its complement to the output. Enable Input Output EECC341 - Shaaban #12 Lec # 9 Winter 2001 1-10-2002 Multiplexers • A multiplexer (MUX) is a digital switches which connects data from one of n sources to the output. • A number of select inputs determine which data source is connected to the output. Enable 1Y D0 Multiplexer EN s bits Select 2Y SEL Data output b bits D0 b bits D1 n Data Sources . . b bits Y D1 . . . . . . bY Dn-1 Dn-1 SEL EN EECC341 - Shaaban #13 Lec # 9 Winter 2001 1-10-2002 4-to-1 MUX Truth table for a 4-to-1 multiplexer: I0 d0 d0 d0 d0 I1 d1 d1 d1 d1 I2 d2 d2 d2 d2 I3 d3 d3 d3 d3 S1 0 0 1 1 S0 0 1 0 1 Y d0 d1 d2 d3 Inputs I0 I1 I2 I3 S1 0 0 1 1 S0 0 1 0 1 Y I0 I1 I2 I3 Inputs 0 4:1 1 MUX Y 2 3 S 1 S0 I0 I1 Output I2 mux Y I3 S1 S 0 select select EECC341 - Shaaban #14 Lec # 9 Winter 2001 1-10-2002 4-to-1 MUX Circuit I0 I0 I1 I1 Y I2 Y I2 I3 I3 0 1 2 3 2-to-4 Decoder S1 S0 S1 S0 EECC341 - Shaaban #15 Lec # 9 Winter 2001 1-10-2002 Larger Multiplexers • Larger multiplexers can be constructed from smaller ones. • An 8-to-1 multiplexer can be constructed from smaller multiplexers as shown: I0 I1 I2 I3 4:1 MUX S1 S0 I4 I5 I6 I7 4:1 MUX 2:1 MUX S2 Y S2 0 0 0 0 1 1 1 1 S1 0 0 1 1 0 0 1 1 S0 0 1 0 1 0 1 0 1 Y I0 I1 I2 I3 I4 I5 I6 I7 S1 S0 EECC341 - Shaaban #16 Lec # 9 Winter 2001 1-10-2002 Larger Multiplexers • A 16-to-1 multiplexer can be constructed from five 4-to-1 multiplexers: EECC341 - Shaaban #17 Lec # 9 Winter 2001 1-10-2002 Standard MSI Multiplexer Example 74151A 8-to-1 multiplexer. EECC341 - Shaaban #18 Lec # 9 Winter 2001 1-10-2002 Demultiplexers • Digital switches to connect data from one input source to one of n outputs. • Usually implemented by using n-to-2n binary decoders where the decoder’s enable line is used for data input of the demultiplexer. Demux b bits Select Data Input One of n Data Sources selected Select lines b bits . . b bits One of n outputs s bits 2X4 Decoder Input data (1bit) One of four 1-bit outputs Enable 1-bit 4-output demultiplexer using a 2x4 binary decoder. EECC341 - Shaaban #19 Lec # 9 Winter 2001 1-10-2002 1-to-4 Demultiplexer Outputs Y0 = D.S1'.S0' Y1 = D.S1'.S0 Data D demux Y2 = D.S1.S0' Y3 = D.S1.S0 S1 So 0 0 0 1 1 0 1 1 Y0 D 0 0 0 Y1 0 D 0 0 Y2 0 0 D 0 Y3 0 0 0 D S1 S0 select Y0 = D.S1'.S0' S1 2x4 Decoder S0 Y1 = D.S1'.S0 Y2 = D.S1.S0' E Y3 = D.S1.S0 D EECC341 - Shaaban #20 Lec # 9 Winter 2001 1-10-2002 Mux-Demux Application Example This enables sharing a single communication line among a number of devices. At any time, only one source and one destination can use the communication line. EECC341 - Shaaban #21 Lec # 9 Winter 2001 1-10-2002