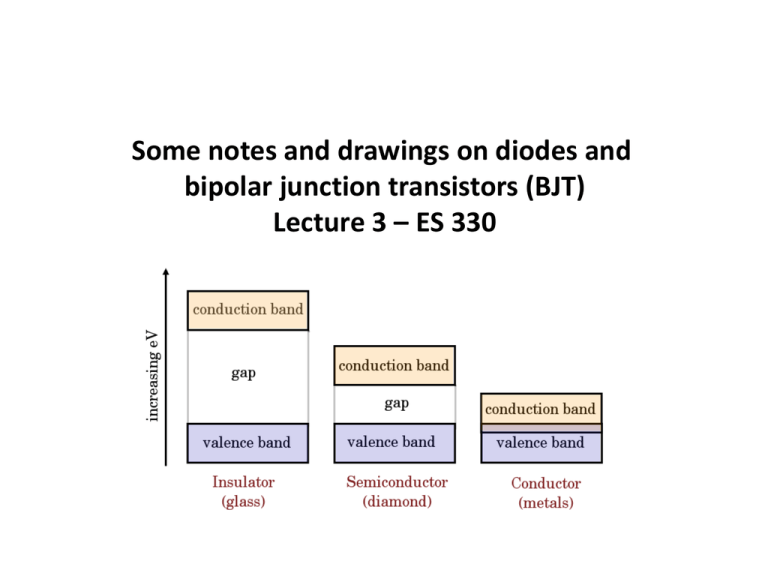

Some notes and drawings on diodes and bipolar junction transistors

advertisement

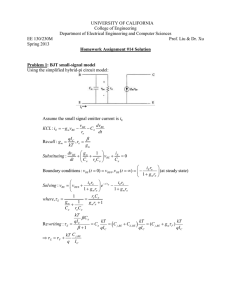

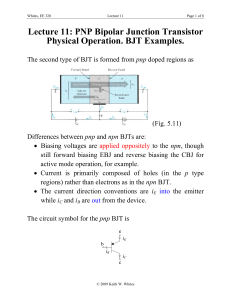

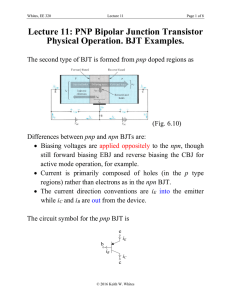

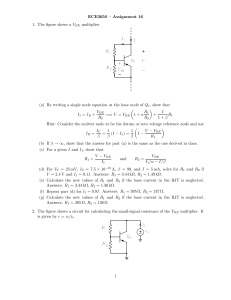

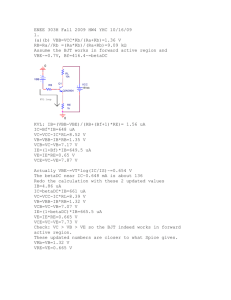

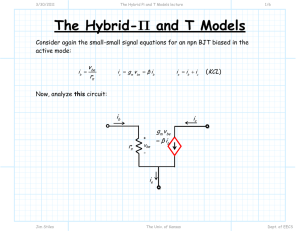

Some notes and drawings on diodes and bipolar junction transistors (BJT) Lecture 3 – ES 330 This is the way we draw an npn bipolar transistor: Planar Process How we envision the electron & hole flow with transistor: Discrete BJTs Fairchild 1959 Designed by Gordon Moore 3-terminal TO-18 Collector contact made from the back of die. Integrated BJTs A bipolar junction transistor cross-section in a planar integrated circuit Collector contact made adjacent topside contact. µA709 operational amplifier Fairchild Semiconductor – 1965 In put Designed by Robert Widlar In put Output First commercial Op Amp to became an industry standard. IC IE g BE IE VTH (For I E =1 mA. = 1 rBE g BE 1 m ) 26 g BE VBE NPN 1 rBE Ebers-Moll Large-Signal Transistor Model IE IES ICS NPN IC Emitter Collector No capacitances included Pay attention to the current directions! RIC IB FIE Base IC αF = IE IE and α R = IC 1 Bipolar Junction Transistor I-V Behavior in Forward Active Region IC “Saturation” Region NPN Increasing VBE Increasing IB “Forward Active” Region VCE No “Early Effect” shown (base width modulation) gm IC Exponential behavior VBE VBE Curve Tracer showing the IC versus VCE characteristics of a BJT Transconductance: gm I C Q 1 Q 1 C VBE r V V r r VBE When I C I S exp VTH 1 , or g m r C I C IC gm VBE VTH Input resistance: VTH r rBE , where rBE IE gm r Input capacitance: C g m r , comes from g m I Q 1 V r V Bipolar Junction Transistor Controlled Charge and Controlling Charge Within Base Region Emitter Origin of Ci within BJT Depletion Layer WB Base Width Base Depletion Layer Collector Forward Base Transit Time WB 2 r 2 Dx Emitter Log (net impurity conc) Base Collector ND NA Nepi 0 WB Depth from surface Hybrid- Model r rbb’ + vb’e r - C C r0 Hybrid- Small-Signal Model for BJT Low-Frequency Hybrid- Small-Signal Model for BJT Hybrid- Model’s Parameters Transconductance gm: gm I C Q 1 Q 1 C VBE r V V r r and g m I C I C VBE VTH Input resistance r: g I B 1 1 I C m r VBE VBE Input capacitance C (= diffusion and depletion layer capacitances): C r gm C jBE EXAMPLE: Small-Signal Model Parameter Values A BJT is biased at IC = 1 mA and VCE = 3 V. =90, r =5 ps, and T = 300 K. Find (a) gm , (b) r , (c) C . Solution: (a) gm IC / (kT / q) 1 mA mA 39 39 mS (millisiemens) 26 mV V 90 2.3 kΩ (b) r / gm 39 mS (c) C F gm 5 1012 0.039 1.9 1014 F 19 fF (femtofarad) From: Modern Semiconductor Devices for Integrated Circuits (C. Hu) Hybrid- Model’s Parameters (continued) Output resistance ro: rO VA VCE IC Typically large wrt load resistance RL where VA is Early voltage Base spreading resistance rbb’: Attenuates input signal & adds noise Resistance from ohmic contact to the edge of the emitter Feedback capacitance (common-emitter configuration) C: C Reverse gmR C jCB Limits bandwidth of CE amplifiers Miller capacitance Feedback resistance (common-emitter configuration) r: g I B 1 1 I E mR r VCB R VCB R Typically ignored because very large Field-Effect Transistors (FET) or Unipolar Transistors JFET Surface carrier inversion at a silicon/silicon dioxide interface N-channel MOSFET transistor Realistic cross-section of n-channel modern MOSFET CMOS – Complimentary Metal Oxide Semiconductor We will use these schematic symbols for MOSFETs N-channel P-channel