Report 4 - Faculty of Information Engineering & Technology

advertisement

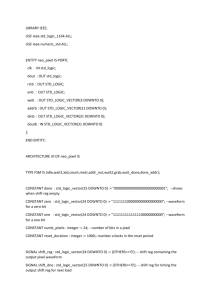

Faculty of Information Engineering & Technology Electrical & Electronics Department Course: Microelectronics Lab ELCT605 Spring 2015 Eng. Salma Hesham Dr. M. Abd El Ghany DIGITAL LAB REPORT 4 MODELING OF SEQUENTIAL CIRCUITS USING VHDL Name ID Grade: Lab Group /10 1 Modeling of Sequential Circuits Using VHDL Lab Task: (Individual Submission) I. 4-bit Right Shift Register II. 4-bit Universal Shift Register 2 Lab Task: I. 4-bit Right Shift Register Fig. 1 Four-bit Right Shift Register 3 a. Which of the following architectures describes the 4-bit right shift register shown in Fig. 1? Entity entity Right_Shift is Port ( clk,reset : in STD_LOGIC; SIR:in STD_LOGIC; Q:out STD_LOGIC_VECTOR(3 downto 0)); end Right_Shift; Architecture #2 Architecture #1 architecture Behav of Right_Shift is begin Process(clk,reset) variable T: std_logic_vector(3 downto 0); begin if(clk'event and clk='1')then if(reset='1')then T:="0000"; else T(3):=SIR; T(2):=T(3); T(1):=T(2); T(0):=T(1); end if; Q<=T; end if; end process; end Behavioral; architecture Behav of Right_Shift is Signal T: std_logic_vector(3 downto 0); begin Process(clk,reset) begin if(clk'event and clk='1')then if(reset='1')then T<="0000"; else T(3)<=SIR; T(2)<=T(3); T(1)<=T(2); T(0)<=T(1); end if; Q<=T; end if; end process; end Behavioral; RTL Schematic #1 RTL Schematic #2 Synthesis Report Information #1 Synthesis Report Information #2 Number of Flip Flops used = Minimum clk period = Maximum frequency = Number of Flip Flops used = Minimum clk period = Maximum frequency = Problem: Problem: 4 b. Modify architecture #1 or architecture #2 to implement the 4-bit right shift register without changing the order of equation assignment. Entity entity Right_Shift is Port ( clk,reset : in STD_LOGIC; SIR:in STD_LOGIC; Q:out STD_LOGIC_VECTOR(3 downto 0)); end Right_Shift; Modified Architecture architecture Behav of Right_Shift is begin end Behavioral; RTL Schematic of 4-bit Right-Shift Register Synthesis Report Information Number of Flip Flops used = Minimum clk period = Maximum frequency = 5 Lab Task: II. 4-bit Universal Shift Register Fig. 1 4-bit Universal Shift Register 1. Tabulate the function of the 4-bit universal shift register based on the provided block diagram in Fig. 1 S1 0 0 1 1 S0 Q3 0 1 0 1 Q2 Q1 Q0 Function 6 2. Multiplexer 4-to-1 Fig. 2 1-bit Mux 4-to-1 A. Create a new source of type VHDL module named “Mux4x1”. Model the 1-bit multiplexer using concurrent when-else or with-select statement. 4-to-1 Multiplexer VHDL code Model Muxes function using Structural port maps modeling Model the register function using behavioral process B. Create a new source of type VHDL module named “Universal_Shift”. Model the function of the Universal Shift register using mixed architectural modeling: Behavioral + Structural as shown in Fig.3. 7 Universal Shift Register VHDL code 8 C. Create a new source of type VHDL Testbench to test the Universal Shift Register using the input test cases provided by Fig. 5. Stimulus Process from the VHDL TestBench code D. Perform a behavioral simulation to check the output according to the provided test cases. Simulation Output 9 E. Synthesize the Code in part (B) to get the RTL schematic, the resources usage and the maximum operating frequency of the design. RTL Schematic Synthesis Report Information Number of Flip Flops used = Minimum clk period = Maximum frequency = 10 F. In terms of the FPGA hardware usage, is the following code more efficient than the code in part (B)? Why? Universal Shift Register VHDL code entity Universal_Shift_2 is Port ( I : in STD_LOGIC_VECTOR (3 downto 0); SIR,SIL : in STD_LOGIC; clk,rst : in STD_LOGIC; s: in std_logic_vector(1 downto 0); Q : out STD_LOGIC_VECTOR (3 downto 0)); end Universal_Shift_2; architecture Behavioral of Universal_Shift_2 is Component LeftShift is Port ( clk,reset,SIL : in STD_LOGIC; Reg_in : in STD_LOGIC_VECTOR (3 downto 0); Q : out STD_LOGIC_VECTOR (3 downto 0)); end component; Component RightShift is Port ( clk,reset,SIR : in STD_LOGIC; Reg_in : in STD_LOGIC_VECTOR (3 downto 0); Q : out STD_LOGIC_VECTOR (3 downto 0)); end Component; Component Load_Reg is Port ( clk,reset : in STD_LOGIC; Reg_in : in STD_LOGIC_VECTOR (3 downto 0); Q : out STD_LOGIC_VECTOR (3 downto 0)); end Component; Component Mux4x1_4bit is Port ( A,B,C,D : in STD_LOGIC_VECTOR (3 downto 0); S : in STD_LOGIC_VECTOR (1 downto 0); F : out STD_LOGIC_VECTOR (3 downto 0)); end component; signal Q_shifted_L,Q_shifted_R:STD_LOGIC_VECTOR (3 downto 0); signal Q_load, Reg_in, Q_temp :STD_LOGIC_VECTOR (3 downto 0); signal S_temp, S_reg :STD_LOGIC_VECTOR (3 downto 0); begin Left: LeftShift port map (clk, rst,SIL, Q_temp, Q_shifted_L); Right: RightShift port map (clk, rst,SIR, Q_temp, Q_shifted_R); Load: Load_Reg port map (clk, rst, Reg_in, Q_load); Load_s: Load_Reg port map (clk, rst, S_temp, S_reg); S_temp <= "00"&S; Reg_in <= I when s="11" else Q_temp; MuxOut: Mux4x1_4bit port map (Q_load, Q_shifted_R, Q_shifted_L, Q_load, S_reg(1 downto 0), Q_temp); Q <= Q_temp; end Behavioral; 11 G. Synthesize the Code in part (F) by downloading and adding all the VHDL sources needed from the eee.guc.edu.eg website. Compare the results with the results in part (E) Synthesis Report Information Number of Flip Flops used = Minimum clk period = Maximum frequency = 12