Gigabit Ethernet Optical Link Design Project

advertisement

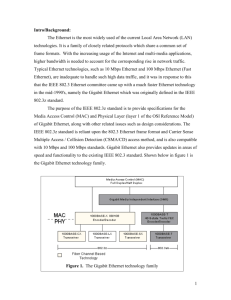

Gigabit Ethernet Optical Link Design Project Group 5: Emily Lyon Spiro Sarris Carlo Espinosa Winston Czakon Eric Woods David Pérez October 24, 2002 School of Electrical and Computer Engineering Georgia Institute of Technology TABLE OF CONTENTS Section Page PROJECT SPECIFICATION 1 GROUP ORGANIZATION 1 BACKGROUND 2 Ethernet 2 Gigabit Ethernet Signals 2 IEEE 802.3z Standard 5 VCSELs and PDs 9 System Level Design Topology 12 PROCEDURE 13 Receiver Test Circuit 13 Optical Link Power Budget 13 VCSEL and Photodetector Specifications 14 Optical Transmitter Design 16 Optical Receiver Design 18 Printed Circuit Board Layout 19 RESULTS 20 ISSUES / DIFFICULTIES 22 PLANNED WORK 23 REFERENCES 24 ii PROJECT SPECIFICATION The purpose of this project is to design and implement an optical transmitter and receiver that comply with the optical Gigabit Ethernet standard IEEE 802.3z. During the course of the project, the group members will follow a task and time management plan created by the group. The design must be carried out on a $350 budget allowance provided by the Georgia Tech ECE department. A system level design topology is provided by the instructors and recommended as guidance for the system design. As an initial step, a receiver board is provided without optical photodetector circuitry. After the electrical-only receiver board is assembled and tested, the group must design photo detector circuitry to integrate with the provided receiver design. Finally, the group will design an optical transmitter circuit intended to interface with the optical receiver. Parts provided include the Maxim 3266 trans-impedance amplifier (TIA), Maxim 3264 limiting amplifier, and the Maxim 3287 laser driver. The signal source used as a pattern generator for testing is the Tektronix GTS1250 GBIC test system. The oscilloscope used for measurements is the Tektronix TDS7154 Digital phosphor oscilloscope. GROUP ORGANIZATION To accomplish the goals of this project, a Gantt chart was created as a timeline of how the work should be divided up and completed. It follows from the chart, shown in Figure 17, that research and gathering information is to continue through the duration of this project. Emily conducted most of the Gigabit Ethernet research with other small contributions from the rest of the group. wk1 8/19 Research Choose VCSEL/PDs Order Parts / wait Assemble Eval Kit Design TX/RX boards Order Passives Design Layout Fabricate boards Assemble TX/RX boards Testing Analyze Results Wriite Paper 1 2nd Design 2nd Layout Second Fab Assemble #2 Second Testing Analyze Results Write Paper 2 wk2 8/26 wk3 9/2 wk4 9/9 wk5 9/16 wk6 9/23 wk7 9/30 wk8 10/7 wk9 wk10 wk11 10/14 10/21 10/28 extended wk12 11/4 wk13 wk14 wk15 11/11 11/18 11/25 wk16 12/2 waiting due due Progress Completed Figure 1: Gantt chart 1 Emily is also responsible for the most of the group management and creation of the Gantt chart. After enough information was gathered on the IEEE 802.3z standards and the specifications of the different components, we were able to start looking for the vendors that would send us the parts in a timely and cost effective manor. The ferrite bead inductors and the 1k and 100k potentiometers ordered by Spiro, the printed circuit boards and VCSELs ordered by Winston and Carlo have arrived, and the photo detector ordered by Eric have arrived. Winston completed most of the assembly of the prefab boards, as he was the most experienced with soldering. Winston also designed the original layout for the transmitter and receiver with Spiro and Carlo also working on the finalization of the design. Winston, Spiro, and David completed the testing of the prefab board. Other critical elements to the design were the optical link budget worked on by Eric, Carlo, Spiro, and David. The assembly of the transmitter board will be completed soon. BACKGROUND Ethernet The Ethernet is a networking protocol that was developed in the early 1970s by Xerox Corporation, initially running at a data rate of 10Mbps. Eventually, Fast Ethernet was developed, increasing the data rate to 100Mbps. With the increasing need of greater speed and more bandwidth, Gigabit Ethernet was considered for development in mid-1995. A Gigabit Ethernet Task Force was created in 1996 that included up to 200 people and 50 companies to develop the necessary components and appropriate standards [1]. The Gigabit Ethernet increased the data rate up to 1000Mbps or 1Gpbs, and was built on top of the existing Ethernet topologies. The Gigabit Ethernet is the same as the original Ethernet from the data layer upwards; below, it combines the IEEE 802.3 Ethernet standard with the ANSIX3T11 FibreChannel standard [1]. This combined the high-speed physical interface with the frame format of the Ethernet to produce a fast, reliable, cost-effective, and scalable networking protocol (NN, Cisco). Gigabit Ethernet Signals The various signals involved in the operation of a Gigabit Ethernet transmitter and receiver can be classified as high or low frequency and high or low sensitivity. The different combinations of these classifications determine amount of care and accuracy required to design an operational circuit. Table 1 indicates the classifications of several of the signals involved in the Gigabit Ethernet link. 2 Sensitivity Frequency High Low High TIA input VCSEL driver outputs Low DC power at DC power at receiver input receiver output Table 1. Classification of signals. In order to preserve the integrity of high frequency signals, the lines on which they travel should be isolated to avoid coupling with other high frequency signals. This can be achieved by keeping the lines spread far apart compared to the height of the dielectric on which they are printed. Transmission line issues must also be taken into consideration to avoid any unwanted resonance or reflections. The simplest solution to the transmission line issue is to make all signal line lengths /10 or less. If the line lengths are this short, then transmission line effects such as phase shifts, reflections, and resonance, are negligible. Various methods of transmission line optimization exist when a line must exceed /10. High sensitivity signals are especially subject to electromagnetic interference (EMI), attenuation, and undesirable coupling. Providing a good return path for the signal can minimize these effects. One way to realize a clear return path is to place connections from the signal and return paths to a ground plane in close proximity in order to prevent crosstalk. However, care must be taken such that coplanar waveguide (CPW) behavior does not couple signals into the substrate. One important performance measurement of digital communications equipment is the bit error rate, or BER. The bit error rate is defined as BER No. _ of _ errors No. _ of _ bits _ sent (Eq. 1) An error is misinterpretation of a logical 1 or 0 value. These errors are a result of numerous problems such as inadequate signal levels, interference, and poorly designed hardware only to name a few. A typical bit error rate for decent Gigabit Ethernet equipment is 10-9 errors/bit or 1 error /Gbit. 3 To determine the maximum lengths of signal lines to use for Gigabit Ethernet hardware, the frequencies of the propagating signals must be determined. The IEEE 802.3z standard for Gigabit Ethernet specifies “Not Return to Zero”, or NRZ, data signals. NRZ means that if a logical 1 is sent immediately following another 1, the signal does not drop to zero between those two instances in time. An example of a NRZ Gigabit Ethernet signal is 1010101, a 500MHz square wave. Using r = 3.0, the wavelength, , is 20cm. So, reasonably, a 2cm line could be treated as a wire in the hardware design. Depending on signal amplitudes and the desired quality of the output signals, higher order harmonics of the square wave dominant frequency signal must be considered. Harmonic No. Frequency Relative Wavelength Maximum Line (f) Amplitude () Length (L) 1 500 MHz 1 20 cm 2 cm 3 1.5 GHz 0.424 6.7 cm 6.7 mm 5 2.5 GHz 0.254 4 cm 4 mm Table 2. Harmonic analysis of 500 MHz square wave To obtain acceptable results without addressing transmission line effects, the fifth harmonic of the data waveform should be considered, and the maximum microstrip line length should be 4mm. A graphical method of measuring the performance of digital hardware is the use of a digital storage oscilloscope to produce an eye diagram. The following setup is implemented to obtain such a diagram. Clock Trigger Pattern Generator Test Circuit Data In Out Figure 2. Setup for producing eye diagrams 4 CH1 Oscilloscope The clock of the signal source or pattern generator triggers the oscilloscope. The signal or pattern is processed by the test circuit, and then enters the oscilloscope on a data input channel. The oscilloscope is set up to acquire a single point, the input level at CH.1, on each clock pulse and display it. After a specified number of points have been displayed, new data points are acquired and the older points are removed from the display. Two examples of eye diagrams are displayed in Figure 3. (a) (b) Figure 3. Example of a good and bad eye diagram. The diagram in 3(a) is very clear because the digital signal levels that the oscilloscope acquires are clearly high or low. The diagram in 3(b) indicates a very poor digital signal. The signal levels that are acquired by the oscilloscope in 3(b) vary between the logical 0 level and logical 1 level. It must be noted that a clear or “open” eye diagram is not necessarily indicative of a low bit error rate. Although the signal levels clearly correspond to a logical 0 or 1 value, an eye diagram shows nothing of whether the value it displays is the correct logical value. IEEE 802.3z Standard The IEEE 802.3z standard was finished and ratified in July 1998. Clause 38 defines the “PMD sublayer and baseband medium, type 1000BaseLX and 1000BaseSX”, which is longwave and short-wave optical transmission for the Gigabit Ethernet respectively. The design project that this group has worked on depends on this standard. In order to begin this task, knowledge and some understanding of the appropriate background and standard were needed. 5 Figure 4. IEEE 802.3z Standard, Clause 38, Section 38.3, Transmit Characteristics The first section in the IEEE 802.3z Standard, Clause 38, that is needed for the project is Section 38.3 “PMD to MDI optical specifications for 1000BASE-SX”. It first defines the operating range and modal bandwidth for both multi-mode (MMF) and single-mode fiber. This project will utilize 62.5m MMF. The standard provides 2 ranges that are specified in Table 382; for 160MHz, the range is 2m-220m, and for 200MHz, and the range is 2m-275m. For this project, testing will be done with a 2m patch cable and a 100m-cable link. There are 3 subsections in 38.3 that specify the transmitter optical specifications, receiver optical specifications, and worst-case power link power budget and penalties. All three of the subsections are relevant to the project, and are shown in Figures 4-6. The parts of the tables that were considered in the design process are highlighted. The wavelength range is defined as 770nm to 860nm; VCSELs that operate at 850nm were chosen for the transmitter board. The other important characteristic is the launch power. The optical link budget, explained in a later section, was verified to meet this specification. 6 Figure 5. IEEE 802.3z, Clause 38, Section 38-3, Receive Characteristics The important characteristic for the receiver is the vertical eye-closure penalty, which indicates the quality of data is coming into the receiver. This determines whether or not a suitable circuit is used to transmit and receive the data. Figure 6. IEEE 802.3z, Clause 38, Section 38-3, Link Power Budget and Penalties. 7 One of the most important specifications in the project is the link power budget, defined in Figure 5. It is the basis for the optical link budget calculations that determine the final design of the transmit and receive boards for this project. The next section that is used for this project is Section 38.5, “Jitter Specifications for 1000BASE-SX and 1000BASE-LX”. These values will be necessary for the testing of the final transmitter and receiver boards, but at this stage in the design process they do not mean much, so the table is not included in this paper. Section 38.6 “Optical measurement requirements” specifies what measurements should be made in testing the equipment, and how they should be made. The measurements that are necessary for this design project include 38.6.5 “Transmitter optical waveform (transmit eye)”, and 38.6.11 “Conformance test signal at TP3 for receiver testing”. The first defines what the transmit data should conform to, i.e. the pulse shape characteristics. The transmitter eye mask definition is shown in Figure 7. Figure 7. IEEE 802.3z, Clause 38, Section 38.6.5, Transmit Eye. The second part of Section 38.6 is the conformance testing. This defines the receive data mask, and how to measure the vertical and horizontal eye-closure, and is shown in Figure 8. These measurements determine whether or not the system being tested is sending acceptable data through the optical link. 8 Figure8. IEEE 802.3z, Clause 38, Section 38.6, Receive Eye Mask This acceptable receive data eye mask is used to measure the data received when testing the transmitter and receiver boards to determine the success and/or failure of the designs. In Section 38.7.2 “Laser Safety,” the required safety standards for the lasers in use are defined. The problem with this section is that it only refers to the IEC 60825-1 eye safety standard, which to this point in time cannot be found. However, the US government does classify laser devices by output power18. Finally, the last relevant section of the IEEE 802.3z standard that is used for this project is Section 38.11, “Characteristics of the fiber optic cabling.” This defines the characteristics of the optical fiber to be used. This includes the modal bandwidth, attenuation, and connection insertion losses associated with the cabling. These characteristics are used in determining optical link budgeting, along with the understanding of the system and how it works. VCSELs and PDs Vertical Cavity Surface Emitting Lasers (VCSELs) and photodiodes (PDs) constitute the physical elements of the optical transceiver system. These components are made from III-V semiconductors – usually gallium arsenide (GaAs) or a ternary combination such as aluminum or indium gallium arsenide. These more advanced materials are required for operation at speeds exceeding 1GHz for two reasons. One is that this class of material is a direct bandgap 9 semiconductor; as such, both components of the transceiver can be fabricated on the same substrate. The other is the significantly higher electron mobility – gallium arsenide has approximately five times that of silicon [16]. This characteristic allows for efficient operation of the devices in extremely high-speed regimes. These lasers have certain metrics that define their performance in any application, such as slope efficiency (η) – the increase in output optical power versus input modulation current (Imod) above the threshold current. The threshold current (Ith) is defined as the minimum current to create a carrier population inversion and to initiate lasing. ITH is linearly temperature dependent with a positive slope, but typically does not shift more than 1mA from the value at the IEEE standard noise temperature of 20˚C, generally 1 – 10mA. These lasers are semiconductors and as such are inherently sensitive to temperature, so there is a maximum safe operation temperature, which is reflected in the maximum modulation current for the device. Design specifications state that for operation of an 850nm laser, the output power cannot exceed 1mW, the limit for a class II laser device as set by the FDA [17]. The heating issues shows how important the series resistance – almost always greater than 20Ω – is to predicting device behavior, and cannot be neglected when modeling the device. This stands in contrast to the standard diode, which generally has negligible series resistance. VCSELs can be modulated at a wide range of speeds, with many artifacts of the power versus current characteristics disappearing at higher speeds. Lasers at high speeds tend to exhibit a relaxation resonance, which produces oscillation on the pulse rising edge. However, VCSELs display a relaxation resonance frequency over 5GHz with an amplitude of the resonance so small as to be difficult to be measured. Other factors that may affect proper VCSEL operation is the turn-on delay which is caused by the rising edge of the optical pulse trailing the rising edge of the electrical pulse by as little as tens of picoseconds. This effect is displayed in Figure 9. 10 Figure 9. Diagram of VCSEL properly biased (left) and biased too far below Ith (right) with a Fiber Channel K28.5 pattern From this, it is clear that the falling edge does not exhibit this delay and therefore the effect of this is width distortion. The most effective way to minimize this effect is to operate at a bias current that is above or close to Ith thus setting an effective minimum for Ibias. Another factor to consider when deigning with VCSELs is the off state bounce. Simply stated, this is caused when the multi-transverse mode structure of VCSELs is used to limit noise and can be minimized by increasing the modulation current. Secondary modes are suppressed on properly aligned fibers, since the VCSEL has smaller transverse modes on the outer edges of the devices, and the fiber is aligned so that only the center desired mode is coupled into the fiber. VCSEL reliability and stability is determined by operating the device well inside the parameters provided by the manufacturer. Typically, circuit values are computed using conservative, worst-case data provided by the manufacturer with built-in compensation circuitry. Photodiodes fundamentally operate as photomultipliers; that is, they amplify incoming photons and create a cascade of carriers that then cause a change in the output device current – typical diode behavior. The use of high-speed devices requires gallium arsenide or similar materials, which in turn limits the types of photodiodes. There are two primary types of photodiodes: junction (p-i-n) and avalanche. Avalanche PDs work by triggering a cascade response to a captured photon through the active region and have very high gains. The downside to this device type is that the response time is low and the sensitivity is not high, which means that it cannot respond fast enough to function at high speeds. Junction photodiodes – specifically p-i-n diodes – have much faster response times and higher sensitivities. The devices have a layer of p-type material, then intrinsic (undoped) material, and finally a layer of n-type material on the bottom. The intrinsic material serves as an excellent amplifier – since it is exactly in balance, large amounts of carriers are quickly moved across the region. However, in practice this region is in constant depletion and creates the device’s parasitic capacitance. In 1GHz optical systems, 11 typical ranges are 1-2pF – anything larger would increase the time constant, depress the device’s operating frequency and bandwidth, and render the device unusable for the desired purpose. In practice, most PDs are made with small active areas so that the capacitance can be minimized, since it is a function of both intrinsic region width and exposed device area. PDs are characterized by their internal quantum efficiency -- the number of carriers generated for each photon absorbed. This number is called the responsivity and has units of amps per watt. Simply, photodiodes are modeled as capacitors in parallel with diodes for high-speed systems. Also, the dark current in photodiodes is important, since it determines the minimum discernable signal (MDS) and thus the sensitivity of the device. The dark current is how much current the device generates under reverse bias when not exposed to light. One common problem shared by VCSELs and PDs is that a phenomenon called ringing can occur if the circuits are not shielded against high-frequency transients. A large blocking capacitor, typically at least hundreds of times larger than the dark capacitance of the PD, is necessary to prevent this ringing. Ringing is a phenomenon caused by having too large of a damping coefficient–above zero--for the circuit – ideally, there should be complete damping of the output when it changes from one amplitude to the other since Gigabit Ethernet uses a notreturn-to-zero (NRZ) encoding scheme. System Level Design Topology Figure 10 shows the top-level design topology suggested by the instructors for this project. Transmitter (TX) Receiver (RX) Optical Fiber Laser Driver VCSEL Photodetector Trans-impedance Amplifier Limiting Amplifier Figure 10. Top-Level Design Topology for Gigabit Ethernet Transmitter and Receiver The VCSEL converts an electrical signal from a laser driver into an optical signal (infrared light), and then radiates that signal through an optical fiber to the PD. The PD takes the optical signal and converts it into an electrical current signal. Connected to the VCSEL is a laser driver 12 chip, which powers the VCSEL and provides it with the signal. The output signal from the PD goes through the TIA, which converts the current to a voltage, and then into the limiting amplifier. The limiting amplifier “cleans up” the digital signal by amplifying all of the input voltages above 4mV to the amplifier saturation voltage of 1.3V at the output [5]. These are the main components used in the transmitter and receiver circuits, and the specifications associated with these determine the passive networks used to control the components. PROCEDURE Receiver Test Circuit Before designing any circuits, the group was provided with a printed circuit board and all of the parts necessary to assemble a receiver circuit with an electrical signal input. The purpose of this exercise was to familiarize the group members with how the board worked, and more importantly with the assembly of the board. The circuit was assembled and tested with the setup in Figure 11. Input Attenuator WW Pattern Generator RX Board Oscilloscope Figure11. Receiver Test Setup The patterns used in this test were PRBS7 and K28.7. For each input pattern, the input attenuation was swept in 10dB steps from 0dB to 60dB. Eye diagrams of the receiver output were recorded for each attenuator step. These diagrams are shown in the Results section. Optical Link Power Budget The objective of the optical link budget is to minimize the power dissipation of the signal from the laser driver to the TIA. The desired output of the VCSEL is to be at the highest possible emitted power that still remains below the Gigabit Ethernet compliant eye safety limit of 1mW. As the current through the VCSEL varies above the VCSEL threshold current, the light intensity increases linearly. The range of current to drive the VCSEL is to be determined. Figure 12 shows a block diagram of the signal flow through the optical components. 13 Iin VCSEL Ieff = Iin - Ith Pout = Ieff* PRX = Pout* PD TIA IPD*R slope efficiency of the VCSEL = attenuation through cable and connectors R = Responsivity of the PD Figure 12. Block diagram of the logical flow for the optical link budget. Table 3 shows a comparison of three different types of VCSELs and the PD that were selected. The range of driver current indicates Iin from Figure 8. This calculation is based on the maximum and minimum values of Ith and . Characteristic Range of Ith (mA) Range of (mW/mA) Desired Emitted Power by VCSEL (mW) Range of Driver Current, Iin (mA) Range of Attenuation Loss (dB) Range of Power Input to PD (mW) Responsivity of Lasermate PD (mA/mW) Range of Current Output to TIA (A) MTR300-N10 4 to 6 .05 (typical) 1 14 to 26 0 to 7.5 0.178 to 1 0.4 72 to 400 HFE4384-522 1.5 to 6 .06 to .3 1 4.8 to 22.6 0 to 7.5 0.178 to 1 0.4 72 to 400 HFE4084-322 1.5 to 6 .1 to .4 1 4 to 16 0 to 7.5 0.178 to 1 0.4 72 to 400 Table 3. Optical Link Budget. VCSEL and Photodetector Specifications The Gigabit Ethernet Standard proposes that the VCSEL and the Photo detector operate at 850nm with a speed of at least 1.25Gbps. In this project, the optical components interface with a 62.5/125m MMF. The connectorized VCSEL and PD will be shipped pre-aligned via an SC connector. The unconnectorized components will require manual alignment to determine their alignment tolerance. The MAX3287 laser driver chip documentation also recommends a common-cathode VCSEL. Table 4 shows a comparison of five different VCSELs. The most important parameters to our applications are the slope efficiency and the threshold current. 14 VCSEL HFE4381-521 MTR300-N10 HFE4384-522 HFE4084-322 OPK210 Manufacturer (mW/mA) Ith(mA) Honeywell 0.04 3.5 Metrodyne 0.05 4 Honeywell 0.15 3.5 Honeywell 0.25 3.5 Optek 0.24 3.5 Connectorized Cost/Unit ($) Yes 19.52 Yes 16.05 Yes 17.65 No 15.75 No 16.82 Note: and ITH are the typical values. Table 4. Comparison of Different VCSELs. The HFE4384-522 was chosen for the connectorized VCSEL because of higher performance, but due to vendor problems, the MTR300-N10 will be utilized first. The two unconnectorized VCSELs in the list have very similar properties, but the HFE4084-322 was chosen considering the cost and availability. Plots of the selected VCSELs emitted power vs. current are shown in Figure 13. Figure 13. Plots of emitted power vs. current: a) MTR300-N10 b) HFE4384-522 c) HFE4084-322 (fig. 13a is not to scale with 13b and 13c) For the PD, a Lasermate GaAs p-i-n PD RSC-M85A306 was chosen because it was the only SC connectorized PD available with a unit cost of $50. These devices have high responsivity and a low capacitance as shown in Table 5, since these characteristics are desirable. The comparable unconnectorized PD, PDT-A85A30, will also be ordered for our unconnectorized PD. 15 Table5. Lasermate RSC M85A306 (top) and PDT-A85A30 (bottom) Optical Transmitter Design Figure 14. Schematic of Optical Transmitter. The optical transmitter circuit was designed according to the specifications, examples, and design equations provided by Maxim in the documentation for the laser driver IC and the specifications of the Honeywell HFE4384-522 VCSEL. 16 Typical Value Slope Efficiency, .15 mW/mA Threshold Current, Ith 3.5 mA Forward Voltage, Vf 1.8 V Table 6. Specifications of Honeywell HFE4384-422 VCSEL First, the total input current to the VSCEL was established to provide maximum light output power within the limitations of the IEC60825-1 eye safety standard. Using a maximum power, Pmax, of 0dBm or 1mW, and of .15 mW/mA, the total input current was calculated from equation 2. Pmax I total I th I total 3.5mA (Eq. 2) 1mW 10.17mA .15mW / mA 6.67mA of the total input current is used to produce light, while the other 3.5mA is used to supply the threshold current. The total current Itotal is composed of a bias current, Ibias, which is equal to Ith, and a modulation (signal) current, Imod. The bias current and modulation current must fit the relationship below in order keep the VCSEL turned on. I bias I th I mod 2 (Eq. 3) While maintaining the input current above the threshold current, Imod was chosen to be 4.2mA peak-to-peak (p-p) to maximize the modulation current. Using this value in equation 3 results in I bias 5.6mA In order to design for Ith possibly being higher than the typical value of 3.5mA, Ibias was chosen to be 5.9mA. The resulting power output of the VCSEL is given by equation 4. Pout ( I bias I mod I th ) (Eq. 4) Pout (.15mW / mA)(5.9mA 4.2mA 3.5mA) 0.99mW Once the bias current and modulation current of the VCSEL were established, the passive component values to be used with the Maxim 3287 Laser Driver were determined. All of the capacitor and inductor values shown in the schematic in Figure 14 were provided by the Maxim 3287 datasheet [7]. The resistor Rvmatch was chosen as 25 to balance the return path (OUT-) with the signal path (OUT+). This is necessary because the signal path includes the 25 series resistance of the VCSEL. The bias current control resistor, Rbias, was determined by Ohm’s law as follows in equation 5. 17 Rbias Rbias Vcc V f I bias (Eq. 5) 5V 1.8V 542 5.9mA The value of the modulation control resistor, Rmod, was calculated according to design equations [7]. Assuming that the load of the VCSEL on the laser driver is 25 1.06 1.15 (1 4.0 10 3 (T 25C ) . (Eq. 6) I mod 51 Rmod 250 RTC 250 When the effects of temperature are not taken into account, RTC is an open circuit and equation 6 reduces to 1.15 I mod 51 . Rmod 250 (Eq. 7) Using Imod = 4.2mA, Rmod 51 1.15 250 13.71k . 4.2mA A 25surface mount resistor was used for Rvmatch, a 1k potentiometer for Rbias, and a 100k potentiometer for Rmod. Optical Receiver Design 400pF Figure 15. Schematic of Optical Receiver The optical receiver circuit was designed according to the material given in the lecture slides by professors Brooke and Jokerst, along in the MAX3266 datasheet [6]. The only change 18 that was made from the class-provided receiver circuit was to replace the electrical signal input with an optical signal input. This was achieved by connecting the anode of a PD to pin 3 and the cathode to pin 4 of the MAX3266 TIA. A 400pF capacitor was placed from the cathode of the PD to ground to stabilize the input signal. Printed Circuit Board Layout The next step in the design project was to take the transmitter and receiver circuits and to create the layout of the Printed circuit board (PCB). ExpressPCB, the company that was used for PCB fabrication, provides free layout software to the customers. After the layout was completed utilizing a specific design procedure that is discussed next, the design was approved by Prof. Brooke, and then submitted to Express PCB for fabrication. The PCB is made of the dielectric FR-4 (flame retarded heat class 4) epoxy glass with 1/2 copper cladding. The size is 2.5 * 3.8 inches, and it uses plated through holes (vias) to connect both sides of the board together. The exposed copper is covered with a tin-lead reflow. The board design includes 0.02in. minimum diameter holes and .012in. line widths. The dielectric constant for FR-4 is relatively high from 4.2 – 5. A problem when using FR-4 at 1GHz is the attenuation, which is 7dB/m (89% loss per meter). This is a concern for high-speed data transfer circuits such as the transmitter and receiver designed in this project, especially at higher 3rd and 5th harmonic frequencies. The attenuation in the lines effectively reduces the input signal range, which can be seen in an eye diagram. Possible improvement to the design could be achieved by decreasing the dielectric constant, thus reducing the loss, by using a ceramic substrate such as LCP instead of an organic substrate like FR-4. The ExpressPCB software has the capability to rotate parts, add vias (automatically add top and bottom pads for vias), cut, paste, create new components, and place traces. The software does not have the capability to analyze the circuit, to easily copy and paste parts on different metal layer, or to rotate parts by a specified angle (other than 90 degrees). However, for the price (free) it is acceptable. 19 The PCBs arrived approximately 3 days after the order. Figure 16 is a picture of the front and back of the circuit board before any assembly took place. To date, no soldering has occurred on these boards. Figure 16. Front and back of printed circuit board received. RESULTS Eye diagrams for the receiver test board (electrical input signal) with input pattern K28.7 are displayed in Figure 17. 20 0 dB 10 dB 20 dB 30dB 40dB 50dB 60dB Figure 17. Eye diagrams for K28.7 pattern with varied input attenuations The eye is slightly degraded when the input signal is attenuated by 50dB, but it still fits the IEEE 802.3z mask. When the input is attenuated by 60dB, the output signal from the receiver can no longer be accurately interpreted as a digital signal. Eye diagrams for the receiver test board (electrical input signal) with input pattern PRBS7 are displayed in Figure 18. 21 0Db 20dB 10dB 30dB 40dB Figure 18. Eye diagrams for PRBS7 pattern with varied input attenuations The output eye diagram for the non-attenuated input signal indicates some jitter that disappears when the input is attenuated by 10dB. The jitter reappears with a 20dB input attenuation and then worsens for 30dB attenuation. When the input signal is reduced by 40dB, it loses its integrity as it passes through the receiver circuit, and the logical 0 and 1 values can no longer be accurately interpreted. The transmitter and receiver circuits described above in the design procedures section have not been assembled and tested yet; therefore, there are no results to present. ISSUES AND DIFFICULTIES Throughout the course of the project period, the group encountered several issues and difficulties that resulted in delayed progress. These issues dealt mainly with acquiring appropriate parts and with group management. The first difficulty encountered with parts was finding a wide variety of VCSELs and PDs with SC connectors. Once components were found, the vendors of these parts only wanted to sell in large quantities. One way to overcome this obstacle was to request free samples. After having placed orders or free sample requests, 22 shipping/delivery times were longer than expected. One package arrived without the connectorized VCSEL that was ordered. The vendor offered to send a similar item as a replacement at no charge due to the initially requested item being out of stock. Several unplanned issues with group management also caused delays in the group’s overall progress. The first was the difficulty in scheduling regular meetings that all of the group members could attend. A meeting time was established on Wednesday evening when no one had any other regularly scheduled responsibilities. Group work was also done in short periods following the class period. With a regular meeting time in place as well as time during and after class periods, there were still two group members who didn’t attend most meetings. Attempts by the four active members to communicate with these two members included numerous emails and several phone calls, most of which were unsuccessful in reaching the goal of maintaining a coherent group in which all members are active and informed. An unbalanced workload resulted from varying levels of effort and attendance by each group member. PLANNED WORK The project described in the Project Specification section of this report has not been completed yet. The information in the Procedure section is indicative of the work that has been completed at this point. A timeline for the projected progress from now until the end of the project period, as well as the timeline of completed tasks, is included in the Gantt chart presented in Figure 1. Remaining tasks that will be completed by the end of the semester include the following: 1. Assemble the transmitter and receiver boards. 2. Test these boards with connectorized VCSELs and PDs. 3. Test them again with unconnectorized VCSELs and PDs 4. Using the group’s unconnectorized transmitter and receiver, measure fiber alignment tolerances of unconnectorized VCSELS and PDs. 23 REFERENCES [1] Introduction to Gigabit Ethernet, Cisco Systems Technology Brief, 1998, http://www.cisco.com/warp/public/cc/techno/media/lan/gig/tech/gigbt_tc.htm [2] Why Optical Ethernet? Nortel Networks, http://www.nortelnetworks.com/corporate/technology/oe/index.html [3]. IEEE Std 802.3, 2000 Edition http://standards.ieee.org/reading/ieee/std/lanman/restricted/802.3-2000.pdf [4] Tektronix GTS1250 Datasheet http://www.tek.com/Measurement/Products/catalog/gts1250/2GW_13513_1.pdf [5] Maxim 3264 Limiting Amplifier datasheet http://pdfserv.maxim-ic.com/arpdf/MAX3264-MAX3765.pdf [6] Maxim 3266 TIA datasheet http://pdfserv.maxim-ic.com/arpdf/MAX3266-MAX3267.pdf [7] Maxim 3287 Laser Driver datasheet http://pdfserv.maxim-ic.com/arpdf/MAX3286-MAX3299.pdf [8] Honeywell HFE4384-522 VCSEL datasheet http://content.honeywell.com:80/vcsel/pdf/HFE4383,4384.pdf [9] Honeywell HFE4084-322 VCSEL datasheet http://content.honeywell.com:80/vcsel/pdf/HFE4083,4084.pdf [10] Honeywell HFE4381-521 VCSEL datasheet http://content.honeywell.com:80/vcsel/pdf/HFE4380,4381.pdf [11] Metrodyne MTR3100-N10 VCSEL datasheet http://www.metrodyne.com [12] LasermateRSC-M85A306 http://www.lasermate.com/ReGaAs.html [14] Modulating VCSELS. Application Sheet http://content.honeywell.com:80/vcsel/technical/006703_1.pdf [15] “How to Solder” http://www.aaroncake.net/electronics/solder.htm 24 [16] Dissertation: Simulation of Heterojunction Bipolar Transistors. Vassil Palankovski. http://www.iue.tuwien.ac.at/publications/PhD%20Theses/palankovski/node43.html [17] Laser Safety Fact Sheet. http://www.uky.edu/Services/EHS/radiation/laser_fs.html [18] FDA PERFORMANCE STANDARDS FOR LIGHT-EMITTING PRODUCTS http://www.accessdata.fda.gov/scripts/cdrh/cfdocs/cfCFR/CFRSearch.cfm?FR=1040.10 25