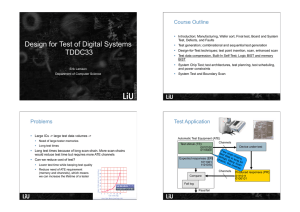

DFT - School of Engineering and Computer Science

advertisement

1 SYLLABUS FOR COURSE DESIGN-FOR-TEST FOR DIGITAL IC'S AND EMBEDDED CORE SYSTEMS Lecturer: Dr. Evgeni Perelroyzen Prerequisites for Course 1.Logic Circuits 2.Optimized Implementation of Logic Functions 3.Number Representation 4.Basic Combinational Circuits 5.Basic Sequential Circuits 6.Computer Structured Organization Aims and Summary This advanced course is designed for the students to be engineers and managers involved in design and testing. The course aims: - to skip the high-brow theories and mathematical formulas – to get down to the business of digital design and testing as it’s done in the real world; - to learn practical testing strategies that address today’s business needs for quality, reliability and cost control, working within the tight deadlines of typical high-pressure production environments. The course helps you optimize the engineering trade-offs between such resources as: - silicon area, - operating frequency, - and power consumption, while balancing the corporate concerns of cost-of-test, time-to-market, and timeto-volume. You’ll also boost your efficiency with the special focus on Automatic Test Pattern Generation (ATPG). Key topics of the course include: - Core-based design, focusing on embedded cores and embedded memories; - System-on-a-chip and ultra-large scale integrated design issues; - AC scan, at-speed scan and embedded design-for-test; - Built-in self-test, including memory BIST, logic BIST and scan BIST; - Virtual test sockets and testing in isolation; 2 - Design for reuse, including reuse vectors and cores; - Test issues being addressed by VSIA(Virtual Socket Interface Alliance) and the IEEE PI500 Standard. Detailed Teaching Plan 1. TEST AND DESIGN-FOR-TEST FUNDAMENTALS [1] 1.1. Introduction to Test and DFT Fundamentals 1.2. The Reasons for Testing 1.3. The Definition of Testing 1.4. Test Measurement Criteria. Complexity of a Test Set [1, 5] 1.5. Fault Modeling [1, 2, 3, 4, 7, 8] - IDDQ Test [2, 3] 1.6. Path Sensitizing. Detection of Specific Faults [1, 7] 1.7. Types of Testing 1.8. Manufacturing Test 1.9. Using Automatic Test Equipment 1.10. Test and Pin Timing 1.11. Manufacturing Test Program Components 2. AUTOMATIC TEST PATTERN GENERATION FUNDAMENTALS 2.1. The Automatic Test Pattern Generation Process [1, 2, 5, 10] - The D-Calculus [2, 9] - A Basic ATPG Algorithm [1, 2, 5] - The PODEM Algorithm [2] - Controllability and Observability [2, 3, 4] 2.2. Testability and Fault Analysis Methods [1, 3, 5, 6, 12, 15, 16] 2.3. Stuck-At, Transition Delay Fault, Path Delay Fault and CurrentBased Fault ATPG [1, 7] 2.4. Combinational versus Sequential ATPG [1, 5] 2.5. ATPG Vectors [1] 2.6. ATPG-Based Design Rules [1, 5] 2.7. How to write testable VHDL code [5] 3. SCAN ARCHITECTURES AND TECHNIQUES 3.1. Introduction to Scan-Based Testing [1, 2, 3, 5, 11] 3.2. Scan Methodology . Full Scan and Partial Scan [1, 5] 3.3. The Scan Shift Register or Scan Chain 3.4. Signature Analysis [1, 7] 3.5. Scan Cell Operations [1] 3.6. Scan-Based Design Rules [1] 3.7. Stuck-At (DC) Scan Insertion [1] 3 3.8. 3.9. At-Speed Scan(AC) Testing [1] Scan-Based Logic BIST (Built-in Self-Test) [1, 2, 3, 7, 17] - LFSR Theory [1, 2] - Signature Analysis [1, 2, 7] - MISR [2] - Built-in Logic Block Observer [7] - Boundary Scan. JTAG Interface [1, 5, 7, 14] - Supplementary test vectors [5] 4. MEMORY TEST ARCHITECTURES AND TECHNIQUES [1, 13] 4.1. Memory Integration Concerns 4.2. Embedded Memory Testing Methods 4.3. The Basic Memory Testing Model 4.4. Algorithmic Test Generation 4.5. Data Retention Test For Memories 4.6. Scan Test Memory Modeling 4.7. Memory Built-In Self-Test Requirements 4.8. MBIST Design-Using LFSRs 5. EMBEDDED CORE TEST FUNDAMENTALS [1] 5.1. DFT Interface Considerations-Test Signals 5.2. Core DFT Interface Concerns-Test Access 5.3. DFT Interface Concerns-Test Wrappers 5.4. DFT Interface Concerns-Test Frequency 5.5. Core DFT Development 5.6. Memory Testing with BIST 5.7. Embedded Test Programs BIBLIOGRAPHY 1. Crouch Alfred L. Design-for-Test for digital IC’s and embedded core Systems.- Prentice Hall PTR, 1999. 2. Smith Michael J.S. Application-Specific Integrated Circuits.- Addison-Wesley, 1997. 3. Kang S.M., Leblebici Y. CMOS Digital Integrated Circuits: Analysis and Design.- McGraw-Hill, 1999. 4. Wolf W.H. Modern VLSI Design: Systems on Silicon(2nd ed.).- Prentice Hall PTR, 1998. 5. Sjoholm S., Lindh L.VHDL for Designers.- Prentice Hall, 1997. 6. Lala P.K. Digital Circuit Testing and Testability.- Academic Press, 1997. 7. Brown S., Vranesic Z. Fundamentals of Digital Logic with VHDL Design.McGraw-Hill, 2000. 4 8. Schoen J.M. Performance and Fault Modeling with VHDL. - Prentice Hall,1988. 9. Chang H.Y., Manning E., Metze G. Fault Diagnosis of Digital Systems.Wiley-Inter-Science,1970. 10. Armstrong James R. Chip-Level Modeling with VHDL.- Prentice Hall, 1989. 11. IEEE Standard Tests Access Port and Boundary-Scan Architecture. IEEE Standard 1149.1-1990. New York: IEEE Standards Board, 1990. 12. Lala P.K. Practical Digital Logic Design and Testing.- Prentice Hall, 1996. 13. van de Goor A.J. Testing Semiconductor Memories: Theory and Practice.Wiley and Sons, 1990. 14. Parker K.P. The Boundary-Scan Handbook(2nd ed.), Analog and Digital.Norwell, MA: Kluwer Academic Publishers, 1998. 15. Abramovici M., Breuer M.A., Friedman A.D. Digital Systems Testing and Testable Design.- IEEE Press, 1995. 16. Tsui F.F. LSI/VLSI Testability Design.-McGraw-Hill, 1987. 17. Rajski J., Tyszer J. Arithmetic Built-In Self-Test For Embedded Systems.Prentice-Hall, 1988. 18. Mazumder P., Rudnick E.M. Genetic Algorithms for VLSI Design, Layout, and Test Automation.- Prentice Hall, 1999. 19. Gulati R.K., Hawkins C.F. IDDQ Testing of VLSI Circuits- A Special Issue of Journal of Electronic Testing: Theory and Applications.- Norwell, MA: Kluwer Academic Press, 1995. 20. Lala P.K. Fault Tolerant&Fault Testable Hardware Design.- Prentice Hall International, Inc. ,1985. 21. Bushnell M.L., Agrawal V.D. Essentials of Electronic Testing for Digital, Memory & Mixed-Signal VLSI Circuits.- Kluwer Academic Publishers, 2001. 22. Navabi Z. Analysis and Modeling of Digital Systems.- McGraw-Hill, 1998. 23. Sivaraman M., Strojw S. A Unified Approach for Timing Verification and Delay Fault Testing, 1997. 24. Stroud C.E. A Designer's Guide to Built-In-Self-Test, 2002.