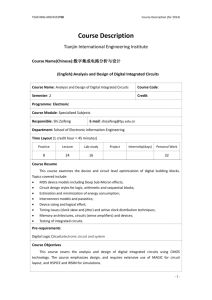

HW5_EE466_F08_Answer..

advertisement

EE 466 (Digital VLSI Design) Homework Assignment # 5 Logic Families Due October 31, 2008 Problem 1: Identifying circuit family a) What type of circuit family has been used for the circuit below? Answer: Precharge-Evaluate (dynamic circuit) b) Provide the equation for the function that this circuit performs. For this purpose take the signal labeled as “pre” to be a clock, also your outputs are D0-3. Answer: D0 S 0 S1 pre, D1 S 0 S1 pre, D2 S 0 S1 pre, D3 S 0 S1 pre c) Provide a timing diagram that shows how signals S0, S1 and “pre” influence the status of the outputs D0-3. Answer: Table: Logic level representation of timing diagram Pre S1 S0 Dout 0 X X 1 1 0 0 D0 0 X X 1 1 0 1 D1 0 X X 1 1 1 0 D2 0 X X 1 1 1 1 D3 The table above provides a timing scheme from which a timing diagram can be derived. The post-layout simulations of the decoder appear below. The D0-3 signals are expected to be at logic 1 during the precharge phase, but because of a poor input latch design, they do not get fully precharged. Problem 2: Using static CMOS a) Using static CMOS please provide a schematic that accomplishes the same function as the schematic of Figure 1. S0 S1 D0 D1 D2 D3 b) Given the fact that static CMOS dissipates less power, has good noise margins and is easy to design, why would you opt to use the logic family used in Figure 1? Answer: The area requirements of the precharge-evaluate circuit are far less than those of static CMOS. c) Provide some shortfalls of the logic family used for the circuit of Figure 1. Answer: Power dissipation increases in dynamic circuits and there is a need for an elaborate input latch to limit short circuit power Problem 3: Ratioed Logic a) Provide the schematic of a 6-input NOR gate in the peudo-NMOS logic style. Answer: 6-Input NOR GATE Vout A B C D E F b) Provide at least two major advantages of this NOR gate over one designed in static CMOS. Answer: It has reduced Fan-In , it requires less area than its static CMOS equivalent, and it switches faster than its static CMOS equivalent. c) It has been stated that static CMOS is easy to design, what do you consider to be the major challenge in designing this pseudo-NMOS NOR gate? Answer: The major challenge is in sizing the CMOS so that it provides good switching speed and reduced short circuit power.