DE_test1 - WordPress.com

advertisement

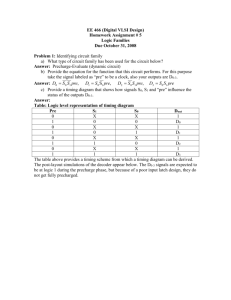

Digital Electronics: Test 1. Saturaed logic circuits have inherently (1) A. Short saturation delay time B. Low switching speed C. Higher power dissipation D. Lower noise immunity 2. The time needed for an output to change from the result of an input change is known as:(1) A. noise immunity B. fan-out C. propagation delay D. rise time 3. How is the noise margin of a logic family defined? (1) A.VOH – VOL B. greater of VDD - VOH and VOL-GND C. Smaller of VIL-VOL and VOH-VIH D. VIH-VIL 4. A TTL circuit acts as a current sink and current source in the …and … respectively. (2) A. Low state and high state B. High state and low state C. High impedance state D. None of these 5. Why is a pull-up resistor needed when connecting TTL logic to CMOS logic? (1) A. to increase the output LOW voltage B. to decrease the output LOW voltage C. to increase the output HIGH voltage D. to decrease the output HIGH voltage 6. CMOS logic family uses only (1) A. MOSFETs & Resistors B. NMOS circuits C. MOSFETs D. bipolar transistors 7. Power is drawn by a CMOS circuit only when (1) A. its output is high B. its output is low C. it switches logic levels D. in static state 1 VIIT, Pune Digital Electronics: Test 8. What type of logic circuit is shown below and what logic function is being performed? (2) A.It is an NMOS AND gate. B. It is a CMOS AND gate. C. It is a CMOS NOR gate. D. It is a PMOS NAND gate. 9. Why is the fan-out of CMOS gates frequency dependent? (2) A. Each CMOS input gate has a specific propagation time and this limits the number of different gates that can be connected to the output of a CMOS gate. B. When the frequency reaches the critical value, the gate will only be capable of delivering 70% of the normal output voltage and consequently the output power will be one-half of normal; this defines the upper operating frequency. C. The higher the number of gates attached to the output, the more frequently they will have to be serviced, thus reducing the frequency at which each will be serviced with an input signal. D. The input gates of the FETs are predominantly capacitive, and as the signal frequency increases the capacitive loading also increases, thereby limiting the number of loads that may be attached to the output of the driving gate. 10. CMOS circuits are extensively used for ON-chip computers mainly because of their Extremely (1) A. low power dissipation. B. high noise immunity. C. large packing density. D. low cost. 2 VIIT, Pune Digital Electronics: Test 11. Special feature of I2L logic circuit is that it (2) A. uses only high value resistors B. dissipates negligible power C. is a bipolar saturated logic D. uses no biasing & loading resistors 12. The logic family which gives complementary output is A. B. C. D. (1) TTL ECL CMOS MOS 13. What is unique about TTL devices such as the 74SXX? (2) A. These devices use Schottky transistors and diodes to prevent them from going into saturation; this results in faster turn-on and turn-off times, which translates into higher frequency operation. B. The gate transistors are silicon (S), and the gates therefore have lower values of leakage current. C. The S denotes the fact that a single gate is present in the IC rather than the usual package of 2–6 gates. D. The S denotes a slow version of the device, which is a consequence of its higher power rating. 14. Using the schematic diagram of a TTL NAND gate, determine the state of each transistor (ON or OFF) when all inputs are high. A. Q1-ON, Q2-OFF, Q3-ON, Q4-OFF B. Q1-ON, Q2-ON, Q3-OFF, Q4-OFF C. Q1-OFF, Q2-OFF, Q3-ON, Q4-ON D. Q1-OFF, Q2-ON, Q3-OFF, Q4-ON 15. The design of a clocked sequential circuit requires A. the state reduction B. the state assignment C. the design of the next state decoder D. all of the above (2) (2) 16. The output of a clocked sequential circuit is independent of the input. The circuit can be represented by (2) A. Mealy Model 3 VIIT, Pune Digital Electronics: Test B. Moore Model C. either Mealy or Moore model D. neither Mealy or Moore model 17. A finite state machine A. is the same as a clocked sequential circuit B. consists of combinational logic circuits only C. consists of electrial motors D. does not exist in practice (1) 18. while constructing a state diagram of sequential circuit from set of given statement, (2) A. a minimum number of states must only be used B. redundant states may be used C. redundant states must be avoided D. none of the above is relevent 19. The number of directed arcs terminating on any state of astate diagram is A. B. C. D. (2) 2n where n is the number of inputs 2n where n is the number of flip-flops in the circuit independent of the number of inputs dependent on the number of outputs. 20. A vertex is a ………..vertex if there are no outgoing arcs which emanate from it and terminate in other vertices. (1) A. Source B. Sink C. node D. none of the above 4 VIIT, Pune Digital Electronics: Test ANSWERS: Question No. Answer 1 A 2 C 3 C 4 A 5 C 6 D 7 C 8 C 9 D 10 C 11 C 12 C 13 A 14 D 15 D 16 B 17 A 18 B 19 C 20 B 5 VIIT, Pune Digital Electronics: Test 6 VIIT, Pune