EEEE 381 Lab 2 MOSFETs - People

advertisement

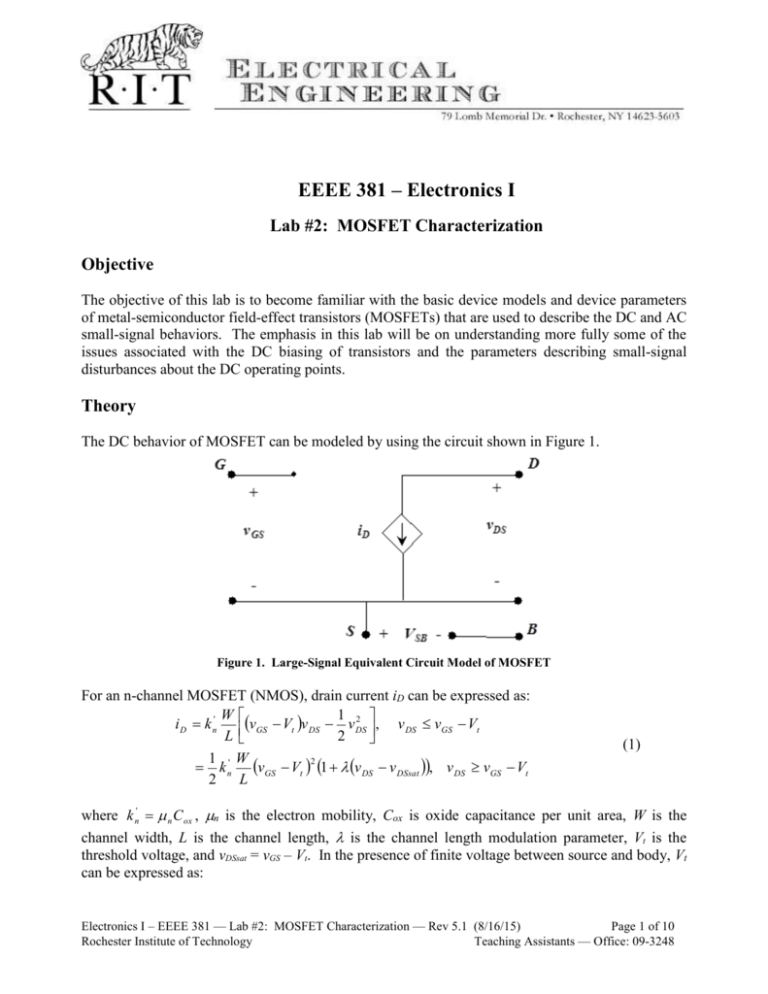

EEEE 381 – Electronics I Lab #2: MOSFET Characterization Objective The objective of this lab is to become familiar with the basic device models and device parameters of metal-semiconductor field-effect transistors (MOSFETs) that are used to describe the DC and AC small-signal behaviors. The emphasis in this lab will be on understanding more fully some of the issues associated with the DC biasing of transistors and the parameters describing small-signal disturbances about the DC operating points. Theory The DC behavior of MOSFET can be modeled by using the circuit shown in Figure 1. Figure 1. Large-Signal Equivalent Circuit Model of MOSFET For an n-channel MOSFET (NMOS), drain current iD can be expressed as: W 2 vGS Vt v DS 1 v DS i D k n' , v DS vGS Vt L 2 1 W vGS Vt 2 1 v DS v DSsat , v DS vGS Vt k n' 2 L (1) where k n' n C ox , n is the electron mobility, Cox is oxide capacitance per unit area, W is the channel width, L is the channel length, is the channel length modulation parameter, Vt is the threshold voltage, and vDSsat = vGS – Vt. In the presence of finite voltage between source and body, Vt can be expressed as: Electronics I – EEEE 381 — Lab #2: MOSFET Characterization — Rev 5.1 (8/16/15) Page 1 of 10 Rochester Institute of Technology Teaching Assistants — Office: 09-3248 Vt Vt 0 2 f VSB 2 f (2) where Vto is the threshold voltage when VSB = 0, f is a physical parameter (typically 2 f = 0.6 V to 2q s N sub 0.8 V) and is the body-effect parameter, where . C ox For a p-channel MOSFET (PMOS), drain current iD can be expressed as: W 1 2 i D k p' v V v v DS , v DS vGS Vt GS t DS L 2 (3) 1 ' W 2 k p vGS Vt 1 v DS v DSsat , v DS vGS Vt 2 L ' where k p p Cox , p is the hole mobility and Vt, Vto, vDSsat , , and are negative quantities. The sign differences between NMOS and PMOS device models are often confusing and take some getting used to. It is worth pointing out, however, that qualitatively the devices behave the same: to have the device on, we require VGS Vt ; to have a device in saturation, we require VDS VDS sat . Channel length modulation in the saturation region of operation ( v DS vGS Vt for NMOS and v DS vGS Vt for PMOS) can be incorporated in the circuit model of Figure 1 through output resistance ro between source and drain. Output resistance ro can be expressed as: |V | 1 (4) ro A | | ID ID where VA is the Early Voltage. If the curves representing the drain current in the saturation region (the portion that is almost horizontal with a slight upward slope) were extrapolated along the drainsource voltage axis, they would theoretically meet at a negative voltage on the axis. The magnitude of this voltage is called the Early Voltage (VA). Electronics I – EEEE 381 — Lab #2: MOSFET Characterization — Rev 5.1 (8/16/15) Page 2 of 10 Rochester Institute of Technology Teaching Assistants — Office: 09-3248 Pre-Lab Before coming to the laboratory, study the Theory section in this lab write-up (also covered in Sections 5.2 and 5.5 in Sedra and Smith (6th ed.) to learn the definitions of threshold voltage Vt , transconductance parameters k and k´, body effect coefficient , and output conductance (channellength modulation) parameter . Before coming to lab, do all of the following: (Note that the TAs may choose to give a short quiz at the start of lab, with questions derived from the required pre-lab work.) (a) Determine what operating region (linear or saturation) the NMOS and PMOS devices of Parts (1) and (2) will be in. Both the NMOS and PMOS devices are enhancement devices. (b) Consider the mathematical model for the current-voltage (I-V) characteristics of the MOSFET and qualitatively sketch the expected appearance of the plots in Part (5). How are the slopes of those plots related to the transconductance parameters? How would you find the threshold voltages, Vt , from the plots? (c) Qualitatively sketch the expected appearance of the plots in Part (6). How are the slopes of those plots related to the body effect coefficient ? (d) Explain how the substrate doping Nsub can be determined once the body effect coefficient is known. (e) Explain how the channel-length modulation factors can be obtained from the plots in Part (8). (f) In preparation for Part (2), refer to Figure 3(b) and calculate/tabulate the VDD values that will be required to give the specified values of VSD. Note that the VSS value (ground) has been specified so as to give the required values of VBS . (g) In preparation for Part (4), refer to Figure 4(b) and calculate/tabulate the VDD values that will be required to give the specified values of VSD . Electronics I – EEEE 381 — Lab #2: MOSFET Characterization — Rev 5.1 (8/16/15) Page 3 of 10 Rochester Institute of Technology Teaching Assistants — Office: 09-3248 Figure 2(a). CD4007 Pin-Out and Specifications Electronics I – EEEE 381 — Lab #2: MOSFET Characterization — Rev 5.1 (8/16/15) Page 4 of 10 Rochester Institute of Technology Teaching Assistants — Office: 09-3248 Figure 2(b). CD4007 continued Electronics I – EEEE 381 — Lab #2: MOSFET Characterization — Rev 5.1 (8/16/15) Page 5 of 10 Rochester Institute of Technology Teaching Assistants — Office: 09-3248 Lab Exercise — Measurement and Calculation of Transistor Parameters In this lab, we will measure certain characteristics of NMOS and PMOS devices that are contained in the CD4007 chip. Refer to Figure 2(a) for the chip pin-out. Pay particular attention to the substrate connections for the NMOS and PMOS devices, pins 14 and 7, respectively. Note that there are three NMOS and three PMOS devices on each chip. The p-substrate connection (pin 7) is common to the NMOS devices; the n-substrate connection (pin 14) is common to the PMOS devices. Some of the gates are internally connected to other transistors (but gate current is zero). It is only necessary to use one NMOS device and one PMOS device for this lab. IMPORTANT: The substrate connections need to be connected to the power supply to create a path for the electrostatic discharge circuitry ESD to ground. Do this before anything is connected to the gates. For the CD4007 chip connect pin 7 to the lowest supply voltage and pin 14 to the highest supply voltage. The gates should be connected last. When deconstructing your circuits, the gates should be disconnected first. Data Collection (Parts (1)–(4)): Part 1: Use the connections shown in Figure 3(a) to measure drain current ID as a function of VDS = VGS for VDS = 0.5, 1, 1.5, 2, 2.5, 3, 3.5, and 4 V for an NMOS device. Make these measurements at VSB = 0, 2, and 5 V (a total of 24 measurements), making sure that the body is negative with respect to the source. Part 2: Use the connections shown in Figure 3(b) to measure drain current ID as a function of VSD = VSG for VSD = 0.5, 1, 1.5, 2, 2.5, 3, 3.5, and 4 V for a PMOS device. The specific values of VDD needed to give the foregoing values of VSD are part of the pre-lab calculations. Make the measurements at VBS = 0, 2, and 5 V (a total of 24 measurements), making sure that the body is positive with respect to the source. If you experience rapidly increasing current for small changes in VSD , you have probably forward-biased the source/substrate junction by incorrectly establishing VBS . Electronics I – EEEE 381 — Lab #2: MOSFET Characterization — Rev 5.1 (8/16/15) Page 6 of 10 Rochester Institute of Technology Teaching Assistants — Office: 09-3248 VDD = variable, from Part (1) >0 ID ID + + VGS – VDS – VSB + – (a) NMOS + VSG – + – VBS VSD + VB = 0, 2, 5 V – VDD = variable, from pre-lab (b) PMOS Figure 3. NMOS and PMOS connections for Parts (1) and (2). VDD = variable, from Part (3) >0 VSS = 2.5 V ID ID + VDS + VGS – (a) NMOS – + + VSG – VSD – VDD = variable, from pre-lab (b) PMOS Figure 4. NMOS and PMOS connections for Parts (3) and (4). Electronics I – EEEE 381 — Lab #2: MOSFET Characterization — Rev 5.1 (8/16/15) Page 7 of 10 Rochester Institute of Technology Teaching Assistants — Office: 09-3248 Part 3: With VSB = 0 V and VGS = 2.5 V, measure drain current ID at VDS = 2, 2.5, 3, 3.5, 4, 4.5, 5, 5.5, and 6 V using the connections shown in Figure 4(a) for an NMOS device. Part 4: With VBS = 0 V and VSG = 2.5 V, measure drain current ID at VSD = 2, 2.5, 3, 3.5, 4, 4.5, 5, 5.5, and 6 V using the connections shown in Figure 4(b) for a PMOS device. The specific values of VDD needed to give the foregoing values of VSD are part of the pre-lab calculations. If you experience rapidly increasing current for small changes in VSD, you have probably forward-biased the source/substrate junction by incorrectly establishing VBS . Data Analysis (Parts (5)–(8)): Assumed data: • tox = 90 nm (90 x 10–7 cm = 0.09 m) and W/L = 100 for both NMOS and PMOS; • approximate value of 2f 0.6 V; a more exact calculation is given as: N sub f 0.0253 * ln at 70F; 10 1.5 x10 (11) Part 5: Plot I D vs. VGS = VDS for both devices at the three values of body bias. Draw the best-fit straight line through your data points. From the intercepts, determine Vt for VSB = 0, 2, and 5 V for each device. From the slope of the VSB = 0 plots, determine the transconductance parameter k = k´W/L . Electronics I – EEEE 381 — Lab #2: MOSFET Characterization — Rev 5.1 (8/16/15) Page 8 of 10 Rochester Institute of Technology Teaching Assistants — Office: 09-3248 Part 6: 2 f VSB 2 f . Determine the body effect parameters () for the For each device, plot Vt vs. NMOS and PMOS devices. Part 7: Estimate the substrate doping Nsub (one value for NMOS and one value for PMOS) by two methods: (1) Use the body-effect parameter calculated in Part (6), the assumed oxide thickness tox, and the body-effect parameter equation to find Nsub; (2) Use the transconductance parameters from Part (5) to determine the carrier mobilities, n and p, then use the following relationship between doping and carrier mobility to determine Nsub: min max min N 1 sub N ref . (12) For electrons (NMOS): 2 min = 68.5 cm2V–1s–1, max = 1414 cm V–1s–1, Nref = 9.20 x 1016 cm–3, and = 0.711. For holes (PMOS): min = 44.9 cm2V–1s–1, max = 470.5 cm2V–1s–1, Nref = 2.23 x 1017 cm–3, and = 0.719. (Alternatively, you may use a graph that relates mobility to doping level, such as that shown in Figure 1.16 of Device Electronics for Integrated Circuits by Muller and Kamins, 3rd ed.) Typically, you will not see good agreement between the values of Nsub determined by the two different methods. The reason for this is that the extraction from the body effect parameter assumes uniform substrate doping, which is not an appropriate assumption for ion-implanted channels. The value of Nsub extracted from may be regarded as an average value that cannot be used to predict carrier mobility and current flow with accuracy. (Capacitive measurement techniques can be used to accurately extract the true doping profile in the substrate.) Part 8: (a) Plot your ID vs. |VDS| data from Parts (3) and (4) for both devices and determine the channel length modulation factors, n and p, from the horizontal intercepts of a straight-line fit to the data. You will see roll-off of the current values at lower |VDS| values, so fit your straight line to the data corresponding to the higher |VDS| values. (b) Use the typical output conductance specifications from Figure 2(b) to find comparative values of n and p, as well as VAn and VAp. Compare these values to your results from Part 8(a) above. Electronics I – EEEE 381 — Lab #2: MOSFET Characterization — Rev 5.1 (8/16/15) Page 9 of 10 Rochester Institute of Technology Teaching Assistants — Office: 09-3248 Check-Off Sheet A. Pre-Lab Determination of NMOS and PMOS operation regions for Parts (1) – (2) of the lab exercise. Sketch of expected appearance of plots in Part (5) of the lab exercise; theoretical relationship of slopes to transconductance parameters k; explanation of how to extract threshold voltage Vt from the plots. Sketch of expected appearance of plots in Part (6) of the lab exercise; explanation of how to extract the body effect coefficient from the plots. Explanation of how to obtain the substrate doping Nsub from the body effect coefficient . Explanation of how to extract the channel-length modulation factors from the plots in Part (8) of the lab exercise. Calculation/tabulation of the VDD values that will be required to give the specified values of VSD in Part (2) of the lab exercise. Calculation/tabulation of the VDD values that will be required to give the specified values of VSD in Part (4) of the lab exercise. B. Experimental Data collection, part (1): Data collection, part (2): Data collection, part (3): Data collection, part (4): NMOS ID as a function of VGS PMOS ID as a function of VSG NMOS ID as a function of VDS PMOS ID as a function of VSD for three values of VSB. for three values of VBS. for fixed values of VGS and VSB. for fixed values of VSD and VBS. *C. Data Analysis (*Optional items for check off during the lab period. Those who complete these items during the lab period will receive the benefit of data and analysis validation by the TA.) Data analysis, part (5): Plots of I D for NMOS and PMOS devices; extraction of threshold voltages Vt and transconductance parameters k. Data analysis, part (6): Plots of Vt vs. 2 f VSB 2 f for NMOS and PMOS devices; extraction of body effect coefficient . Data analysis, part (7): Estimation of substrate doping Nsub by two methods for NMOS and PMOS devices. Data analysis, part (8): Plots of ID vs. |VDS| data for NMOS and PMOS devices; extraction of channel length modulation factors, n and p; comparison to values obtained from data sheet. TA Signature: ____________________________ Date: ___________________________ Electronics I – EEEE 381 — Lab #2: MOSFET Characterization — Rev 5.1 (8/16/15) Page 10 of 10 Rochester Institute of Technology Teaching Assistants — Office: 09-3248