Proposed - Si-EPIC

advertisement

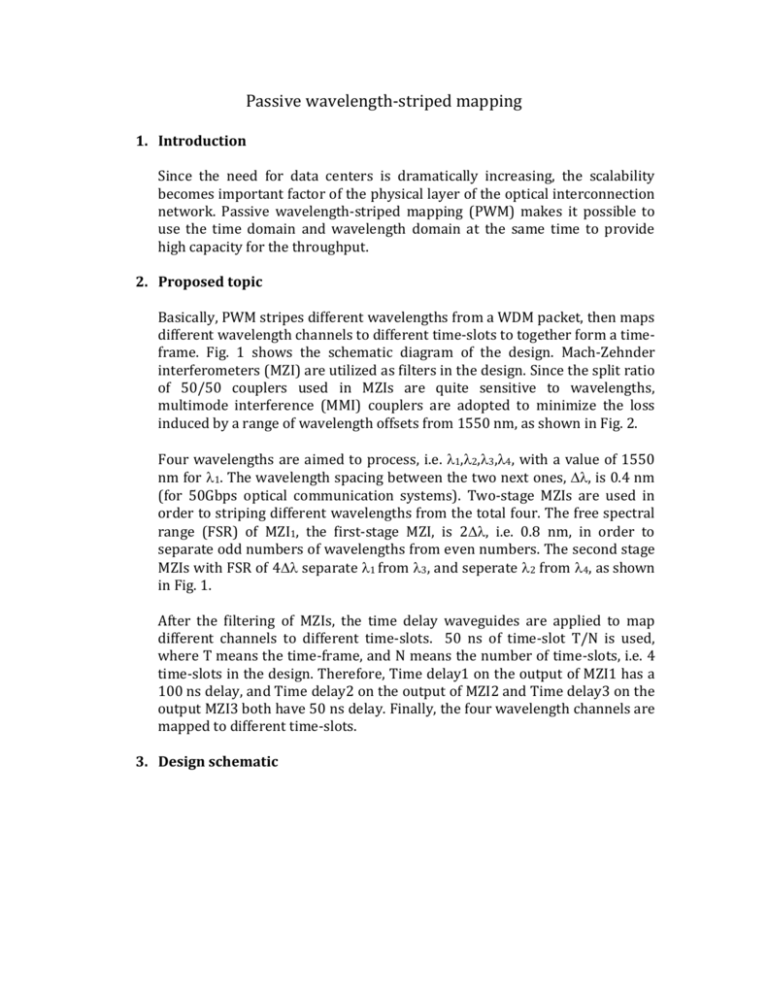

Passive wavelength-striped mapping 1. Introduction Since the need for data centers is dramatically increasing, the scalability becomes important factor of the physical layer of the optical interconnection network. Passive wavelength-striped mapping (PWM) makes it possible to use the time domain and wavelength domain at the same time to provide high capacity for the throughput. 2. Proposed topic Basically, PWM stripes different wavelengths from a WDM packet, then maps different wavelength channels to different time-slots to together form a timeframe. Fig. 1 shows the schematic diagram of the design. Mach-Zehnder interferometers (MZI) are utilized as filters in the design. Since the split ratio of 50/50 couplers used in MZIs are quite sensitive to wavelengths, multimode interference (MMI) couplers are adopted to minimize the loss induced by a range of wavelength offsets from 1550 nm, as shown in Fig. 2. Four wavelengths are aimed to process, i.e. 1,2,3,4, with a value of 1550 nm for 1. The wavelength spacing between the two next ones, , is 0.4 nm (for 50Gbps optical communication systems). Two-stage MZIs are used in order to striping different wavelengths from the total four. The free spectral range (FSR) of MZI1, the first-stage MZI, is 2, i.e. 0.8 nm, in order to separate odd numbers of wavelengths from even numbers. The second stage MZIs with FSR of 4 separate 1 from 3, and seperate 2 from 4, as shown in Fig. 1. After the filtering of MZIs, the time delay waveguides are applied to map different channels to different time-slots. 50 ns of time-slot T/N is used, where T means the time-frame, and N means the number of time-slots, i.e. 4 time-slots in the design. Therefore, Time delay1 on the output of MZI1 has a 100 ns delay, and Time delay2 on the output of MZI2 and Time delay3 on the output MZI3 both have 50 ns delay. Finally, the four wavelength channels are mapped to different time-slots. 3. Design schematic FSR=4 1, t=0 MZI2 1,2,3,4 FSR=2 1,3 3, t=T/N MZI1 FSR=4 2,4 Time delay2=T/N 2, t=2T/N MZI3 4, t=3T/N Time delay1=2T/N Time delay3=T/N Fig. 1 Schematic of design L MMI MMI (a) Structure of MZI1 L/2 (b) Structure of MZI2 Fig. 2 Structure of MMI and MZI3 MZIs MMI 4. Modeling 3D FDTD will be used for modeling waveguides in different lengths, 1*2 and 2*2 MMIs separately. After making sure all of them work properly, MZIs will be modeled using MODE. Then three MZIs and three time delay waveguides will be modeled together with MODE. 5. Parameters The path difference of MZI1 L: Since 𝜆2 𝐹𝑆𝑅 = = 0.4 𝑛𝑚 𝑛𝑔 ΔL where 𝜆 = 1550𝑛𝑚, 𝑑𝑛 𝑛𝑔 = 𝑛 − 𝜆 𝑑𝜆 = 3.476 − 1550𝑛𝑚 ∗ (−7.6 ∗ 10−5 𝑛𝑚 ) = 3.594, ΔL = 1.078𝜇𝑚 Therefore, the path difference of MZI2 and MZI3 L/2=0.539𝜇𝑚. Time delay waveguide1: Core(Silicon) For Silicon 𝑛𝑔 = 3.594 (wavelength = 1550 nm), in order to have Time delay1 = 100 ps, Length = 100 ps*c/𝑛𝑔 =8.347 mm where c is the light velocity in free space. Width = 2.8μm, Thickness = 0.8μm Cladding(SiO2) Length = 8.347 mm, Width = 6μm, Thickness = 2.5μm Time delay waveguide2 and 3: Length = 8.347mm/2=4.174mm Use the same values as Time delay waveguide1 for the other sizes. Therefore, the maximum loss due to Time delay waveguides is experienced 3𝑑𝐵 by 4. It’s approximately calculated as 1𝑐𝑚 ∗ 12.521𝑚𝑚 = 3.756 𝑑𝐵, which is acceptable. 6. Parameter variations Design 1: 1,2,3,4 FSR=2 1,3 MZI1 2,4 Time delay1=2T/N Fig. 3 Schematic of Design 1 Design 2: FSR=4 MZI2 1,2,3,4 FSR=2 1,3 MZI1 2,4 1, t=0 3, t=T/N Time delay2=T/N FSR=4 2, t=2T/N MZI3 4, t=3T/N Time delay1=2T/N Time delay3=T/N Fig. 4 Schematic of Design 2