MAC - 914 - NIT Arunachal Pradesh

advertisement

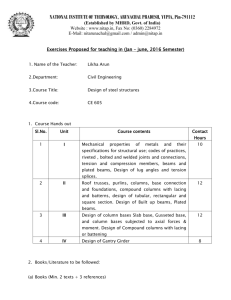

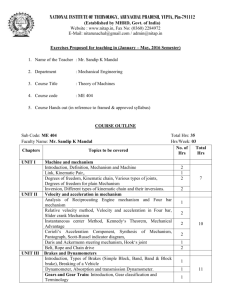

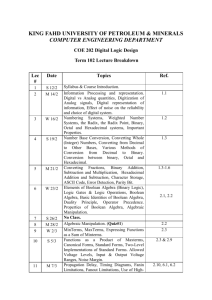

NATIONAL INSTITUTE OF TECHNOLOGY, ARUNACHAL PRADESH, YUPIA, Pin-791112 (Established by MHRD, Govt. of India) Website : www.nitap.in, Fax No: (0360) 2284972 E-Mail: nitarunachal@gmail.com / admin@nitap.in Exercises Proposed for teaching in (July – December, 2015 Semester) 1. Name of the Teacher: Subhasish Banerjee 2. Department: Computer Science and Engineering 3. Course Title: Binary Arithmetics & Logic operations 4. Course code: MAC - 914 1. Course Hands out (in reference to framed & approved syllabus) (maximum 500 words) ____________________________________________________________________ Course Contents Unit 1: Number Systems: Decimal, Binary, Octal and Hexadecimal systems, conversion of a number from one base to another. Codes: BCD, Excess- 3, Gray, Reflected, ASCII, EBCDIC. Algebra for logic circuits: Logic variables; Logic constants; Logic functions- NOT, AND, OR, NAND, NOR, Ex-OR; Combinational circuits : Full Adder / Subtractor, BCD Adder, LAC Adder, Comparator, Decoder, Encoder, Priority Encoder, MUX/DEMUX & there structures ,Combinational logic design using ROM, PLA array, Applications of MSI designs. Boolean Algebra and Switching Functions: Basic postulates and fundamental theorems of Boolean algebra; Standard representation of logic functions - SOP and POS forms; Simplification of switching functions - K-map and Quin McCluskey tabular methods; Combinatorial Logic Systems: Definition and specification; Truth table; Basic logic operation and logic gates, Synthesis of combinational logic circuits, Combinational Logic Modules and their applications: Decoders, encoders, multiplexers, demultiplexers and their applications; Parity circuits and comparators; Arithmetic modules- adders, subtractors and ALU; Design examples. Sequential Logic systems: Basic sequential circuits- latches and flipflops: SR-latch, D-latch, D flip-flop, JK flip-flop, T flip-flop Unit II: Data Representation; Register, Transfer and Micro operations, Basic Computer Organization, Classification of computer architecture: SISD, SIMD, MISD, MIMD, And Instruction Cycle Forma. Contact Hours 8 hrs 12 hrs NATIONAL INSTITUTE OF TECHNOLOGY, ARUNACHAL PRADESH, YUPIA, Pin-791112 (Established by MHRD, Govt. of India) Website : www.nitap.in, Fax No: (0360) 2284972 E-Mail: nitarunachal@gmail.com / admin@nitap.in Unit III: The ALU: ALU organization, Integer representation, Serial and Parallel Adders, is 1s and 2s complement arithmetic, Multiplication of signed binary numbers, floating point number arithmetic, Overflow detection, Status flags. Instruction formats, Addressing modes, Instruction execution with timing diagram. Unit IV: Addressing types, I/O Organization, Memory Organization and managements techniques, Multiprocessors and its architecture. 2. Books/Literature to be followed: (a) Books (Min. 2 texts + 3 references) (i) Title Author Publisher Edition Digital Design and Computer Design M. M. Mano Pearson First Edition (ii) Title Author Publisher Edition Computer Organization and Architecture William Stalling Pearson Eighth Edition (iii) Title Author Publisher Edition Computer System Architecture M. M. Mano Pearson Third Edition (iv) Title Author Publisher Edition Computer Architecture and Organization N. P. Carter Tata McGraw Hill (Schaum’s Outline) Second Edition (v) Title Author Publisher Edition Fundamental of Digital Circuit Anand Kumar Prentice Hall of India Second Edition 10 hrs 10 hrs NATIONAL INSTITUTE OF TECHNOLOGY, ARUNACHAL PRADESH, YUPIA, Pin-791112 (Established by MHRD, Govt. of India) Website : www.nitap.in, Fax No: (0360) 2284972 E-Mail: nitarunachal@gmail.com / admin@nitap.in (b) Magazines/Journals (Minimum 5) (i) IEEE Micro Magazines, IEEE Computer Society, United State. (ii) IEEE Transactions on Computers, IEEE, Computer Society, United State. (iii) ACM Transactions on Computing Systems (TECS), ACM newyork, United State. (iv) Journal of Systems Architecture, Elsevier, Netherlands. 7. Mode of Teaching: J.C Bose/S. N. Bose (please tick). S. N. Bose 8. If the course is of practices, list the experiments to be offered. i). Realization of NOT, OR, AND, XOR & XNOR gates using universal gates a. To study Gray to Binary conversion & vice-versa. b. To study Code conversion between BCD and EXCESS-3 ii). a. Realisation of odd and even parity and checking of Truth Tables. b. Design of a 4-bit comparator circuit & verification of its truth tables. iii). Design of combinational circuit to drive seven-segment display iv). Design of combinational circuits using multiplexer to show that MUX is universal logic circuits. v). a. Study of Full-Adder/Full-Subtractor using IC and/ or logic gates. b. To study BCD Adder circuit using IC and/or logic gates vi). Realization of RS, JK, and D flip flops using Universal logic gates. vii). Design Ripple Carry Adder viii). Design Carry-look-ahead adder ix). Design Registers and Counters x). Design Wallace Tree Adder xi). Design Combinational Multipliers xii). Design Booth's Multiplier xiii). Design Arithmetic Logic Unit Are the manuals ready for the experiments to be conducted? Yes Remarks/ Endorsement by the HoD With his /her signature with date Name of the Teacher: Subhasish Banerjee Designation: Assistant Professor Signature with Date: