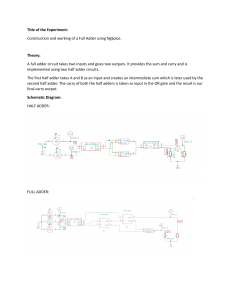

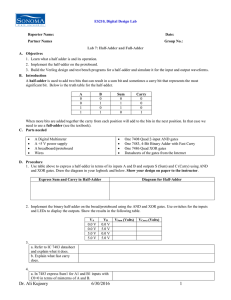

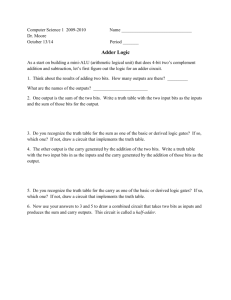

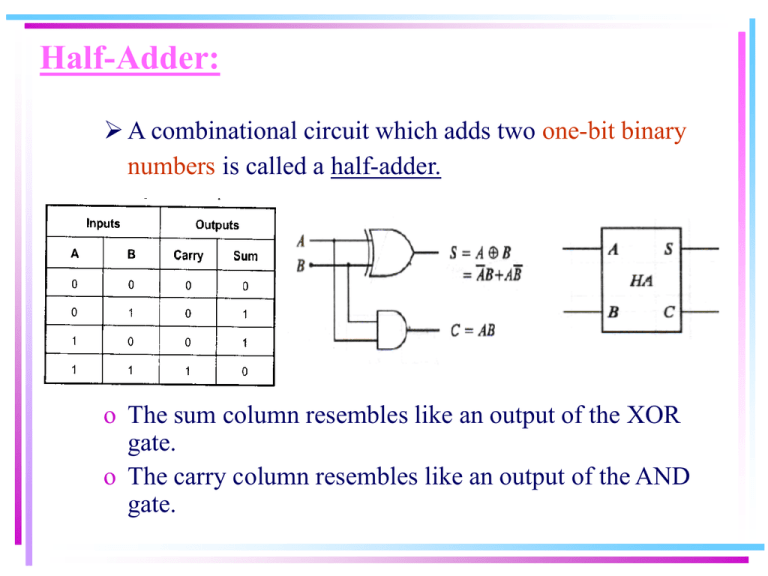

Half-Adder

advertisement

Half-Adder: A combinational circuit which adds two one-bit binary numbers is called a half-adder. o The sum column resembles like an output of the XOR gate. o The carry column resembles like an output of the AND gate. Limitations (disadvantages) of half-adder: o In multi-digit addition we have to add two bits along with the carry of previous digit addition. Such addition requires addition of 3 bits. This is not possible in half-adders. Full Adder: o In a full adder, three bits can be added at a time. The third bit is a carry from a less significant column. Alternate Representation of Full-Adder: Parallel Binary Adder o While we add the LSB, there is no carry to be handled and thus, only a half adder is used for this stage. o For any other bit addition, there may be a carry from the preceding stage and thus, full adders are used for these stages. Example: