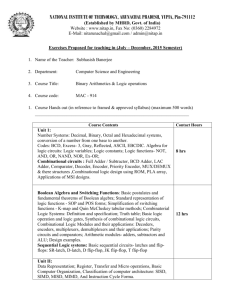

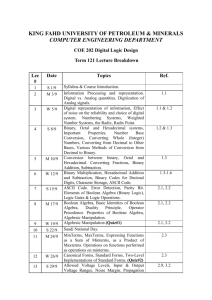

Chapter 4 Combinational Logic

advertisement

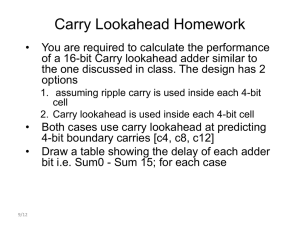

Combinational Logic Chapter 4 1 Combinational Circuits Combinational Circuits • Adders • Subtractors • Comparators • Decoders • Encoders • Multiplexers Available as MSI Circuits and as Standard Cells in VLSI (Bonus Assignment: Get one example of each type of combinational circuits in the CMOS family, 5 points for the second exam) Analysis Procedure • Given a logical diagram, determine one or more of the following: – Boolean functions; – Truth table; – Explanation of circuit operation • Make sure the circuit is combinational, not sequential (No feedback loops) Analysis Procedure 1. Label all gate outputs that are a function of input variables. Determine the Boolean function for each gate output 2. Label the gates that are a function of input variables and previously labeled gates. Find the Boolean functions for these gates 3. Repeat step 2 until output of circuits are obtained 4. By repeated substitution of previously defined functions, obtain the output Boolean functions in terms of input variables Analysis Procedure Analysis Procedure Step 1 𝑇2 = 𝐴𝐵𝐶 𝑇1 = 𝐴 = 𝐵 + 𝐶 𝐹2 = 𝐴𝐵 + 𝐴𝐶 + 𝐵𝐶 Step 2 𝑇3 = 𝐹2′ 𝑇1 𝐹1 = 𝑇3 + 𝑇2 Steps 3 and 4 𝐹1 = 𝑇3 + 𝑇2 = 𝐹2′ + 𝐴𝐵𝐶 = 𝐴𝐵 + 𝐴𝐶 + 𝐵𝐶 ′ 𝐴 + 𝐵 + 𝐶 + 𝐴𝐵𝐶 = 𝐴′ + 𝐵′ 𝐴′ + 𝐶 ′ 𝐵′ + 𝐶 ′ 𝐴 + 𝐵 + 𝐶 = 𝐴𝐵𝐶 = 𝐴′ + 𝐵′ 𝐶 ′ 𝐴𝐵′ + 𝐴𝐶 ′ + 𝐵𝐶 ′ + 𝐵′ 𝐶 + 𝐴𝐵𝐶 = 𝐴′ 𝐵𝐶 ′ + 𝐴′ 𝐵′ 𝐶 + 𝐴𝐵′ 𝐶 ′ + 𝐴𝐵𝐶 Analysis Procedure 1. Determine the number of input variables in the circuit. For 𝑛 inputs, form the 2𝑛 possible input combinations and list the binary numbers from 0 to 2𝑛 − 1in a table 2. Label the outputs of selected gates with arbitrary symbols 3. Obtain the truth table for the outputs of those gates which are a function of the input variables only 4. Proceed to obtain the truth table for the outputs of those gates which are a function of previously defined values until the columns for all outputs are determined Analysis Procedure Design Procedure 1. From the specifications of the circuit, determine the required number of inputs and outputs and assign a symbol to each 2. Derive the truth table that defines the required relationship between inputs and outputs 3. Obtain the simplified Boolean functions for each output as a function of the input variables 4. Draw the logical diagram and verify correctness of the design Code conversion example Code conversion example Code conversion example 𝑧 = 𝐷′ 𝑦 = 𝐶𝐷 + 𝐶 ′ 𝐷′ = 𝐶𝐷 + 𝐶 + 𝐷)′ 𝑥 = 𝐵′ 𝐶 + 𝐵′ 𝐷 + 𝐵𝐶 ′ 𝐷′ = 𝐵′ 𝐶 + 𝐷 + 𝐵𝐶 ′ 𝐷′ = 𝐵′ 𝐶 + 𝐷 + 𝐵(𝐶 + 𝐷)′ 𝑤 = 𝐴 + 𝐵𝐶 + 𝐵𝐷 = 𝐴 + 𝐵(𝐶 + 𝐷) Code conversion example Binary Adder-Subtractor Half adder 𝑆 = 𝑥 ′ 𝑦 + 𝑥𝑦′ 𝐶 = 𝑥𝑦 Half adder Full adder Full adder Implementation of full adder in sum-of-products 𝑆 = 𝑥 ′ 𝑦 ′ 𝑧 + 𝑥 ′ 𝑦𝑧 ′ + 𝑥𝑦 ′ 𝑧 ′ + 𝑥𝑦𝑧 𝐶 = 𝑥𝑦 + 𝑥𝑧 + 𝑦𝑧 Full Adder Full adder Implementation of full adder using two half adders and one or gate 𝑆 = 𝑧 ⊕ (𝑥 ⊕ 𝑦) = 𝑧 ′ 𝑥𝑦 ′ + 𝑥 ′ 𝑦 + 𝑧(𝑥𝑦 ′ + 𝑥 ′ 𝑦)′ = 𝑧 ′ 𝑥𝑦 ′ + 𝑥 ′ 𝑦 + 𝑧(𝑥𝑦 + 𝑥 ′ 𝑦 ′ ) = 𝑥𝑦 ′ 𝑧 ′ + 𝑥 ′ 𝑦𝑧 ′ + 𝑥𝑦𝑧 + 𝑥 ′ 𝑦 ′ 𝑧 𝐶 = 𝑧 𝑥𝑦 ′ + 𝑥 ′ 𝑦 + 𝑥𝑦 = 𝑥𝑦 ′ 𝑧 + 𝑥 ′ 𝑦𝑧 + 𝑥𝑦 Binary adder Carry propagation Full Adder with 𝑃 and 𝐺 shown Carry Generate Carry propagation 𝑃𝑖 = 𝐴𝑖 ⊕ 𝐵𝑖 𝐺𝑖 = 𝐴𝑖 𝐵𝑖 𝑆𝑖 = 𝑃𝑖 ⨁𝐶𝑖 𝐶𝑖+1 = 𝐺𝑖 + 𝑃𝑖 𝐶𝑖 𝐶0 = input carry 𝐶1 = 𝐺0 + 𝑃0 𝐶0 𝐶2 = 𝐺1 + 𝑃1 𝐶1 = 𝐺1 + 𝑃1 𝐺0 + 𝑃𝑜 𝐶0 = 𝐺1 + 𝑃1 𝐺0 + 𝑃1 𝑃0 𝐶0 𝐶3 = 𝐺2 + 𝑃2 𝐶2 = 𝐺2 + 𝑃2 𝐺1 + 𝑃2 𝑃1 𝐺0 + 𝑃2 𝑃1 𝑃0 𝐶0 Carry lookahead generator Four-bit adder with carry lookahead Carry lookahead generator Four-bit adder with carry lookahead Binary subtractor Overflow • Occurs only when adding two positive numbers or two negative numbers; • Overflow produces change in result sign Example: eight-bit adder Carry bits 0 1 1 0 +70 0 1000110 -70 1 0111010 +80 0 1010000 -80 1 0110000 +150 1 0010110 -150 0 1101010 Decimal Adder • Consider adding two decimal digits in BCD • Output sum cannot exceed 9+9+1=19 (the last 1 is the carry from previous digit) Decimal Adder Need correction Carry 𝐶 = 𝐾 + 𝑍8 𝑍4 + 𝑍8 𝑍2 Condition for correcting result Decimal Adder Binary Multiplier Exercise: Multiply 10 × 11 Explain how you carried the multiplication out. How many bits at the output? Binary Multiplier Two-bit multiplier Binary Multiplier Exercise: With your neighbor classmate discuss its operation. Magnitude Comparator Exercise: Discuss with your neighbor classmate and write down how you would compare two four-bit binary numbers 𝐴 and 𝐵, where 𝐴 = 𝐴3 𝐴2 𝐴1 𝐴0 and 𝐵 = 𝐵3 𝐵2 𝐵1 𝐵0 . You should have three outputs corresponding to 𝐴 = 𝐵, 𝐴 > 𝐵, and 𝐴 < 𝐵. Explain how you determined each condition. Magnitude Comparator Does this circuit correspond to what you wrote down in the exercise? Discuss again with your neighbor classmate the comparison of your result with this circuit. Decoders Exercise: Minimize the functions for two of the eight output lines. Decoders Exercise: Compare your function with the circuit. Three-to-eight-line decoder Decoders 0 Decoders 4 × 16 decoder constructed with two 3 × 8 decoders Exercise: Explain how this decoder works. Combinational logic implementation Exercise: For the maps of the full adder shown above, express the sum 𝑆 (left) and the carry bit 𝐶 (right) as a sum of minterms. Combinational Logic Implementation 𝑆 𝑥, 𝑦, 𝑧 = (1,2,4,7) 𝐶 𝑥, 𝑦, 𝑧 = (3,5,6,7) Compare in terms of propagation time and number of gates this Full Adder with the previously studied implementation. Encoders 𝑧 = 𝐷1 +𝐷3 +𝐷5 + 𝐷7 𝑦 = 𝐷2 +𝐷3 +𝐷6 + 𝐷7 𝑥 = 𝐷4 +𝐷5 +𝐷6 + 𝐷7 Priority encoder Highest priority Valid output Priority encoder Exercise: obtain the function for 𝑉 Priority encoder Multiplexers • Selects binary information from one of many input lines • Directs input line to output, controlled by a set of selection lines • 2𝑛 input lines and 𝑛 selection lines Multiplexers Two-to-one-line multiplexer Multiplexers Four-to-one-line multiplexer Multiplexers Quadruple two-to-one-line multiplexer Boolean function implementation • Multiplexer is essentially a decoder with OR gates • Thus can implement Boolean functions, similar to decoders • Minterms generated by circuit associated with selection inputs • Individual minterms can be selected by data inputs • Boolean function of 𝑛 variables and 2𝑛 data inputs Boolean function implementation • More efficient method for implementing a Boolean function of 𝑛 variables with multiplexer of 𝑛 − 1 selection inputs • Remaining variable of function is used for the data inputs Boolean function implementation • Example: 𝐹 𝑥, 𝑦, 𝑧 = (1,2,6,7) Selected input line 0 1 2 3 Implementation of a three-input Boolean function Boolean function implementation 𝐹 𝐴, 𝐵, 𝐶, 𝐷 = 0 1 2 3 4 5 6 7 (1,3,4,11,12,13,14,15) Three-state gates Three-state gates Multiplexers with three-state gates Homework Assignment • • • • • • 4.3 4.9 4.17 4.27 4.33 Using LogicWorks, simulate a 4-bit full adder with and without carry-lookahead.