Project I: Ultra-short Channel InGaAs Transistors and In situ TEM

advertisement

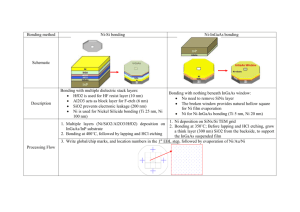

IEBL weekly progress report Student Name: Renjie Chen Project I: Ultra-short Channel InGaAs Transistors and In situ TEM Study of Ni-InGaAs Reactions Project II: Self-defined Ni-InGaAs Contact for III-V MISFET on Si Week of 07/29/2013 – 08/11/2013 Summary: In these two weeks, I was focusing on the InGaAs TEM sample preparation. I broke a lot of the 500um membrane windows, but the new TEM grids with 100um membrane improves a lot on the chance of unbroken windows. I was planning to go over all the process this time to get an idea of what problems I may face, so got a kind of rush this time and the sample surface became very ugly after three times EBL writing. I felt that dealing with the TEM grids need more patient and carefulness, PMMA is not easily cleaned up after each step, which may requires a MMA primer layer and a void of rewriting in each step. The Ni etching from the backside is not done yet. I will continue on the process and try some new samples with more carefulness. Project I: Ultra-short Channel InGaAs Transistors and In situ TEM Study of Ni-InGaAs Reactions 1. Ni silicide bonding on Si TEM aperture frame: Regarding the Ni-silicide bonding, I recently did a lot samples on Si wafer for Yun Goo/Atsunori’s project, but none of the samples are good for use. Here lists the bonding condition I used. Dielectric Layers HfO2/Al2O3/SiO2 (10nm/10nm/200nm) HfO2/SiO2 (10nm/200nm) HfO2/SiO2 (10nm/200nm) Results 10 samples separated either during lapping or during HCl etch. The samples bonded with TEM grid are always successful. Only 4/10 samples have small pieces InGaAs transferred. The samples bonded with TEM grid are always successful. I cut the Si piece smaller than the InGaAs before bonding, and the bonding was successful. It’s very strange that the smaller Si piece compared with InGaAs can always bond well but not the larger Si pieces, even though Daisy did at the same time with me. I was suspecting that the ALD deposited HfO2 recently had some problem, and I also observed some holes on this HfO2 surface after RIE etch in the following steps. 2. Processing with new TEM grids: With new TEM grids that have 9 small windows atop, the membranes are never easily broken. However, I did observe some humps on the membrane, which I think is due to the out-gassing of PMMA from the bottom. IEBL weekly progress report Figure 1: Microscope images of bonded samples. (a) the 9 windows increase the chances of unbroken windows. (b) some distortion/humps are observed after HCl etch, but interestingly none of these distorted membrane broke during the process. In previous design the markers and supporting lines were written in the first layer followed by Ni/Au/Ni evaporation. These Ni/Au/Ni lines are used as both the supporting frame and the diffusion sources. The advantage of doing this is that it can save a step of EBL, which decreases the chance of breaking the membrane. However, the drawbacks of doing this are that the Au may also diffuse into InGaAs, and that the metal lines may influence the dose for Fin writing with HSQ (shown in Fig 2). (a) (b) (c) Figure 2: Previous design of writing the Ni lines first and then the Fin structures atop. (a) large-scale uniformity. (b) and (c) show the fin structures after RIE etching. The fin width was enlarged because of the influence of the metal lines on the dose or due to the off focusing with the membrane. As we discussed to change back to standard 3-step EBL processing (markers, fins and then Ni pads), I tried on the new TEM grids. IEBL weekly progress report Figure 3: Fin structures on TEM membrane. The width of fins varies from 20nm to 200nm, and length from 1um to 5um. It’s found that if the membrane is distorted, the fins are either not written or with uncontrollable width, which is due to the off focusing. When doing RIE etch, I realized that some etched holes formed on the HfO2 layer, especially the edge of windows, which lead to a break of the window in following multiple O2 plasma/HF treatment. (a) (b) Figure 4: SEM image of the same TEM window before (a) and after (b) RIE etch. It might be due to the over etch in RIE step or the thinner (10nm) HfO2 layer I used here. Due to 3 times EBL writing, lift-off, RIE etch, and multiple O2 plasma/HF treatment, the TEM windows look very ugly with seldom pieces of good InGaAs fins remaining there (shown in Fig 5). IEBL weekly progress report Figure 5: Ugly surface after all processing. Lift-off is always a problem with the small sample, and the distorted membrane window caused trouble for fin writing. I was planning to go over all the process this time to get an idea of what problems I may face, so got a kind of rush this time. I felt that dealing with the TEM grids need more patience and carefulness, PMMA is not easily cleaned up after each step, which may requires a MMA primer layer and avoiding re-writing in each step. The Ni etching from the backside is not done yet. I will continue on the process and try some new samples with more carefulness. 3. Diffusion test on InGaAs/Insulator/Si substrate: Per our discussion to check the diffusion on bulk substrate before doing the TEM, I did some test on the bonded InGaAs/insulator/Si substrate. It can be found that larger line width requires less dosage, while smaller features need more dosage. And once the line width is below 100nm, it’ll need a circular line at the edge to support the fins. I’m going to try with the even lower dose, while write the narrow fins 3-4 times. Dose = 1300uC/cm2 Width = 1um Width = 500nm Width = 200nm Width = 500nm Width = 200nm Width = 50nm Dose = 1000uC/cm2 Width = 1um Figure 6: Concentric lines with different line width. The EBL was down yesterday, and I haven’t got chance to write the Ni pad in the center for diffusion test. This will be done in the next week. Project II: Self-defined Ni-InGaAs Contact for III-V MISFET on Si 1. Modified Ni-InGaAs bonding with new photo-mask: In the new designed photo-mask, Ni pads are more densely compacted with less interspacing. The bonding temperature can now be lowered down to 250 C for 20min. Fig 1 (a) and (b) illustrate the uniform surface after InGaAs transferring. IEBL weekly progress report (a) (c) (b) (d) (e) Figure 1: Ni-InGaAs bonding at 250’C for 20min. (a) and (b) shows the uniform surface after bonding. (c)-(e) are the gaps between S/D with designed distance of 1um, 1.5um, and 2um respectively. It can be seen that the distances between S/D is slightly (around 200-300 nm) larger than our designed value due to the mask fabrication deviation. However, the extension of Ni-InGaAs alloy (indicated in the shallow regions) brings the gap into shorter distance, and the estimated diffused length is around 200nm from each side at this bonding condition. A remaining probability? associated with the next alignment step is the offset of markers, which may lead to the misalignment of all top structures when writing with EBL in the following steps. (a) (b) Figure 2: Misalignment of markers. It seems that the offset of alignment markers is not consistent with each sample, and with certain samples the misalignment is too large, while with others it’s acceptable. IEBL weekly progress report I was planning to cut Si wafer into larger pieces, because the edge height differences are severe with my previous small samples. Edge-bead removal is also needed in order to improve the alignment. Plan for Next Week: - When will Yun Goo and Atsunori require the bonding samples? Daisy also faced the bonding failure last week, and we haven’t figure out the reason yet. - The TEM membrane samples require really carefulness, especially that I need to write three times EBL and do the RIE on it. When I tried to rush or do multiple tasks at the same time, I always ruined the samples. So I planed to focus on the TEM sample fabrication first, and hope to finish the sample in this week, so that I can have some sample for TEM measurements and I’ll focus on the TEM training and measurements on the week of August 19th. - The diffusion test on bonded InGaAs/Insulator/Si substrate can be done in parallel.