Project I: Self-defined Ni-InGaAs Contact for III

advertisement

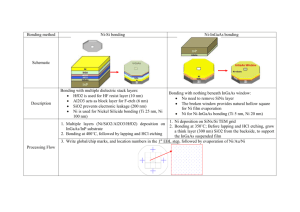

IEBL weekly progress report Student Name: Renjie Chen Project I: Self-defined Ni-InGaAs Contact for III-V MISFET on Si Project II: Ultra-short Channel InGaAs Transistors and In situ TEM Study of Ni-InGaAs Reactions Week of 07/15/2013 – 07/28/2013 Summary: In these two weeks, two projects are performed in parallel. For the selfdefined Ni-InGaAs S/D transistors, modified bonding condition was tested with thinner Ti/Ni layers. It was found that with 5nm Ti/20nm Ni the bonding was successful and that a thin layer of unreacted InGaAs layer remains atop of the Ni-InGaAs which can act as a protection layer for Ni-InGaAs alloy from being etched by HCl or HF. On the other hand, the InGaAs was successfully transferred onto Si TEM aperture frame by carefully controlling the HCl etching & rinsing steps. Multiple steps of EBL are done on the TEM grid to write the markers, Ni lines, and the Fin structures. The membrane window survives these steps, and the sample is going to be ready for TEM observation after ClICP etch and removal of dielectric layers from the backside. Project I: Self-defined Ni-InGaAs Contact for III-V MISFET on Si 1. ZEP 520A E-beam Resist Test: Per our previous discussion, we may want to figure out a way to define the Fin structures without using HSQ, because the multiple O2 Plasma/ BOE steps may attack the bonded Ni-InGaAs. ZEP 520A was chosen for this test, because of its higher resolution compared to SU8, and stronger etching resistance compared to PMMA. Though it’s positive resist, inversed pattern could be used to write the Fins, and this resist is widely used in Peide Ye’s group for InGaAs Fin patterning. Here lists the recipe I used: 1. Si/SiO2 wafer cleaning: solvent clean and O2 plasma 2. ZEP 520A coating: 4000rpm × 60s, 500rpm/s 3. Bake at170°C for 5min 4. EBL writing with the Fin width varying from 20nm to 100nm 5. Development: ZED-N50 (n-Amyl acetate) 5min at 4°C 6. Rinse with IPA The as-span ZEP 520A has a thickness at 460nm, measured by the Surface Profier. According to the dose test, the pattern could be completely developed only if the dose is larger than 280 uC/cm2, and the accessible minimum Fin width is around 60 nm, because the Fin may collapse with even reduced width. IEBL weekly progress report (a) ~ 60 nm Fin Dose = 300 uC/cm2 (b) ~ 50 nm Fin Dose = 290 uC/cm2 Figure 1: ZEP 520A dose test. With dose larger than 280 uC/cm2, the pattern shows a clean surface after development. However, the minimum fin width I can reach here is 60 nm (a), and below that the Fins will collapse (b). The probable reason for Fin collapse is its high aspect ratio, so I also tried with diluted ZEP 520A (1:1 diluted in Anisol). Under the same spin speed and baking condition, the resulted film thickness is ~ 150nm. According to dose test, the minimum total dosage for effective exposure should be larger than 250 uC/cm2, giving a smallest Fin size of 3040nm. Total Dose = 250 uC/cm2 Figure 2: Diluted ZEP 520A (1:1 in Anisol) dose test. The smallest fin width is 30~40 nm and the dosage here is 250uC/cm2. Previously, Daisy applied multiple times writing technique in her Fin writing with HSQ and realized that the 2 times writing gives a sharper edge. Initiated by this idea, I also tried to write with multiple layers but fixing the total dosage to be 260uC/cm2. IEBL weekly progress report 1 Layer × 260 uC/cm2 3 Layer × 85 uC/cm2 4 Layer × 65 uC/cm2 2 Layer × 130 uC/cm2 5 Layer × 50 uC/cm2 Figure 3: Multiple layers writing with diluted ZEP 520A (1:1 in Anisol). The total dose was fixed at 250-260 uC/cm2, and the number of layers varies from 1 to 5 layers. It’s shown in the image that better line profile can be achieved by writing more than 3 times. Since ZEP 520A can be used for 30nm Fin writing by half diluted in anisol, the next question to test is how the ZEP resist can stand Cl-ICP etching. Covered by half piece of ZEP 520A with thermal tap, the patterned sample was test in Cl-etching with ICP 230W/PIE 30W for 100s, which is the maximum etching time for InGaAs in the same condition. However, after Cl-etching, the 150nm ZEP film (diluted ZEP) was totally gone and a thickness of 190nm was removed from the thicker ZEP film (original ZEP) – estimated etching rate: 1.9nm/s. (a) (b) IEBL weekly progress report Figure 4: Cl-etching test on ZEP 520A. For this test, the ZEP 520A was not diluted, and the film thickness decreased 190nm after 100s Cl-ICP. The SEM images show the 100nm fin structure (a) before etching, and (b) after etching. It can be seen from Fig 4 that the ZEP pattern was totally destroyed by the Cl-etch, which is not suitable for the Fin structure fabrication. Since currently the HSQ procedure is the most mature and routine recipe for fin definition, I would prefer to figure out a way to protect the Ni-InGaAs from HF attack while still keep using HSQ in the process. One way that I thought out was to have a thin layer of InGaAs unreacted with Ni, which can act as a protection layer for Ni-InGaAs alloy from been etched by HCl or HF. 2. Modified Ni-InGaAs bonding process: In the previous attempts, the bonding was performed with metal stacking layers of 20nm Ti/50nm Ni. It was found that the Ni-InGaAs surface is quite rough after HCl etching, and there’re always cracks in between InGaAs and Ni-InGaAs, which might be caused by HCl attacking. One way I thought out to solve this problem is to employ thinner Ti/Ni layers that will not fully react through the 50nm InGaAs layer, so the unreacted InGaAs thin layer can act as a protection layer for Ni-InGaAs alloy from been etched by HCl or HF. (a) Cracks (b) Figure 5: Previously transferred samples, bonded with 20nm Ti/50nm Ni. The bonding happened at (a) 400’C, and (b) 350’C. The rough surfaces indicate the reacted Ni-InGaAs, and there’re always cracks in between InGaAs and Ni-InGaAs. (a) (b) (c) IEBL weekly progress report (d) (e) (f) Figure 6: Modified transferring process, bonded with 20nm Ti/50nm Ni. (a) shows the transferred InGaAs piece, and some cracks happened in the marker regions where there’re large hollow area. (b) and (c) show the typical gap between source and drain. (d)-(f) clearly proves that there’s a certain thickness of unreacted InGaAs layer. As the cracks problem has been solved, I think it’s readly to write some fin structures in between the S/D regions. The unreacted thin InGaAs layer atop can also protect the NiInGaAs from HF etching during the HSQ removal steps. Project II: Ultra-short Channel InGaAs Transistors and In situ TEM Study of Ni-InGaAs Reactions 1. Processing Flow: As has been discussed, the process flow that currently works is with multiple dielectric layers stack. The structure is illustrated in the schematic below. Figure 7: Schematic for InGaAs transferring onto Si TEM aperture frame. The detailed stacks are as follow: HfO2 is used for HF resist layer (10 nm) Al2O3 acts as block layer for dry F-etch (6 nm) SiO2 prevents electronic leakage (200 nm) Ni is used for Nickel Silicide bonding (Ti 25 nm, Ni 100 nm) Several issues remained to be solved: 1. How to control the InGaAs orientation in bonding & EBL steps? IEBL weekly progress report One possible solution I was thinking of is to align the TEM grid edge with the InGaAs wafer edge during bonding, and to align the TEM window edge with EBL stage. However, the bonding requires short time to put wafers together and load into RTA, so it’s hard to achieve. The other possible solution is that we don’t care about the bonding and EBL orientations, but write the Fins in different angles(0 degree to 45degree, and 5 degree in increment). Since all possible orientations are present, the TEM will define their accurate crystalline orientations. 2. Is the etching from the backside controllable to stop at a thin layer of HfO2? In order to have a better control of the etching, ICP/RIE is a better choice to remove the dielectric layers from the backside. To better understand the etch rate, etching tests were done with the Cl/F –etch equipment here. Cl-etch F-etch Recipe InP_ICP SiO2_ICP_NO O2 SiO2 11nm/min 240nm/min Al2O3 X X SiNx 12nm/min 360nm/min X – not detectable compared with measurement errors It can be seen from the table that F-etch can quickly remove SiO2 layer while the Al2O3 can efficiently block the further etching. 2. Current processing status: After modifying the HCl etching and rinsing steps, the window breaking issue is relatively solved. As-transferred InGaAs layer showing a shinning green color (without 6nm Al2O3) or shinning yellow color (with 6nm Al2O3). (a) (b) (c) Figure 8: Microscope images of current process status. (a) as-transferred InGaAs layer on TEM aperture. (b) after marker and Ni lines writing. (c) after Fin structures writing. Plan for Next Week: - Prepare the bonded samples for Yun Goo and Atsunori. - Perform Cl-etch to get the Fin structures, and remove dielectric layers from the backside. If Minh got some TEM time, I can follow him to test the Ni diffusion. - Arrange TEM training with Katie, and prepare more TEM samples for later test - Denise will finish the photomask fabrication on Tuesday, and then I can try the Fin writing for the self-defined S/D devices.